小梅哥和你一起深入學習FPGA之串口調試(一)(下)

那么,特權同學在這里有通過注釋解釋為什么是12個波特率周期:“我們的標準接收模式下只有1+8+1(2)=11bit的有效數據”。即使是11位,小梅哥還是無法理解為什么需要12個波特率時鐘。我們在實際使用的時候,一般不去考慮校驗位的問題,因此總共只有10位,也就是說,我寫的10位數據位的仿真模型和特權的11位方式不兼容。考慮到大多數的應用過程中是10位,因此小梅哥在特權大神的代碼上稍作修改,以適應10位模式。這里,將第52行代碼“else if( num==4'd12 ) begin ”改為“else if( num==4'd10 ) begin ”,將第86行代碼“else if( num == 4'd12 ) begin”改為“else if( num == 4'd10 ) begin”。通過這樣更改,就能夠適應1bit的數據接收。同時,小梅哥在實際調試中發現,第45行的“bps_start_r <= 1'bz ;”代碼也存在問題,在復位時,給了bps_start_r一個高阻態,這樣在實際仿真時,會導致錯誤,因此小梅哥在這里,將這一行代碼進行了修改,復位時將bps_start_r置為0,即修改為“bps_start_r <= 1'b0 ;”。

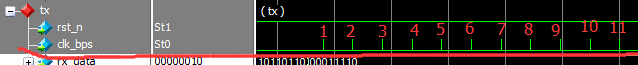

本文引用地址:http://www.104case.com/article/283060.htm以上為接收部分的修改。發送部分的波特率波形如下所示:

同樣有11個波特率時鐘,因此,小梅哥將發送部分的代碼稍作修改,以適應10bit的數據發送。特權同學原始代碼如下:

41 always @ ( posedge clk or negedge rst_n ) begin

42 if(! rst_n ) begin

43 bps_start_r <= 1'bz ;

44 tx_en <= 1'b0 ;

45 tx_data <= 8'd0 ;

46 end

47 else if( neg_rx_int ) begin //

48 bps_start_r <= 1'b1 ;

49 tx_data <= rx_data ; //

50 tx_en <= 1'b1 ; //

51 end

52 else if( num==4'd11 ) begin //

53 bps_start_r <= 1'b0 ;

54 tx_en <= 1'b0 ;

55 end

56 end

57

58 assign bps_start = bps_start_r ;

59

60//---------------------------------------------------------

61 reg rs232_tx_r ;

62

63 always @ ( posedge clk or negedge rst_n ) begin

64 if(! rst_n ) begin

65 num <= 4'd0 ;

66 rs232_tx_r <= 1'b1 ;

67 end

68 else if( tx_en ) begin

69 if( clk_bps ) begin

70 num <= num+1'b1 ;

71 case ( num)

72 4'd0 : rs232_tx_r <= 1'b0 ; //

73 4'd1 : rs232_tx_r <= tx_data [0]; // bit0

74 4'd2 : rs232_tx_r <= tx_data [1]; // bit1

75 4'd3 : rs232_tx_r <= tx_data [2];// bit2

76 4'd4 : rs232_tx_r <= tx_data [3]; // bit3

77 4'd5 : rs232_tx_r <= tx_data [4];// bit4

78 4'd6 : rs232_tx_r <= tx_data [5]; // bit5

79 4'd7 : rs232_tx_r <= tx_data [6]; // bit6

80 4'd8 : rs232_tx_r <= tx_data [7]; // bit7

81 4'd9 : rs232_tx_r <= 1'b1 ; //

82 default : rs232_tx_r <= 1'b1 ;

83 endcase

84 end

85 else if( num==4'd11 ) num <= 4'd0 ; //

86 end

87 end

88

這里,我們將第52行代碼“else if( num==4'd11 ) begin”修改為“else if( num==4'd10 ) begin”,將第85行代碼“else if( num==4'd11 ) num <= 4'd0 ;”修改為“else if( num==4'd10 ) num <= 4'd0 ;”同樣,第43行,針對“bps_start_r <= 1'bz;”也進行了與接收部分相同的修改,即修改為“bps_start_r <= 1'b0 ;”其他部分不變,然后再進行仿真編譯測試。仿真結果如下:

由以上仿真結果可知,通過修改,該串口模塊已經能夠實現正確的收發了。接下來,小梅哥將通過板級驗證來對該模塊進行測試。

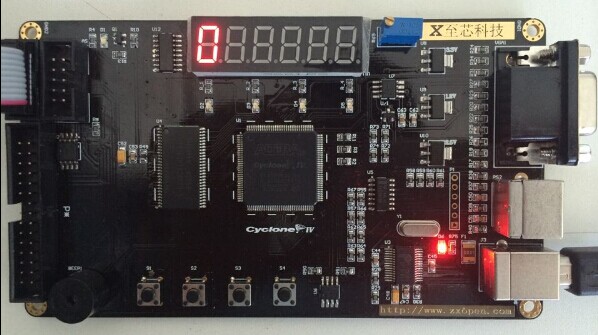

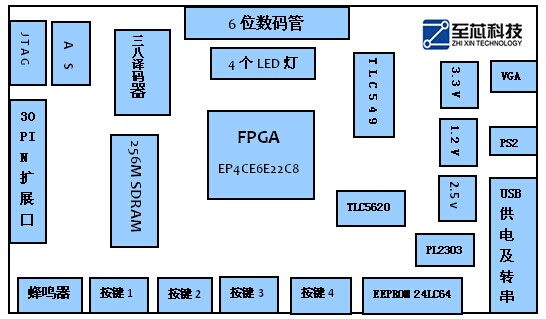

這里,小梅哥使用至芯科技提供的一塊入門級FPGA開發板來完成該模塊的板級驗證。以下為該開發板的照片:

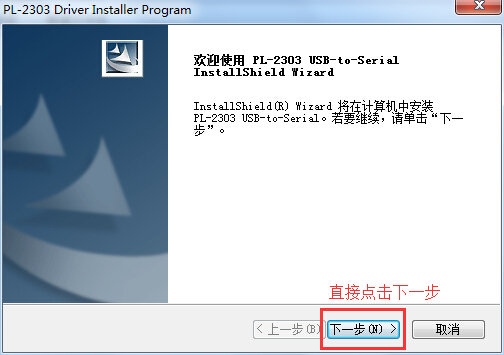

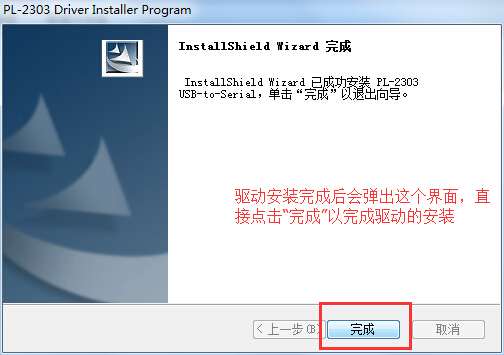

該開發板上集成了一枚PL2303的USB轉串口芯片,因此,我們不再需要笨拙的9針串口線,只需要一根USB線將開發板與電腦的USB口相連,再安裝PL2303的驅動,即可在PC端模擬出一個串口端口,該串口端口的使用和傳統串口端口沒有任何差別。具體的串口驅動安裝過程如下圖所示:

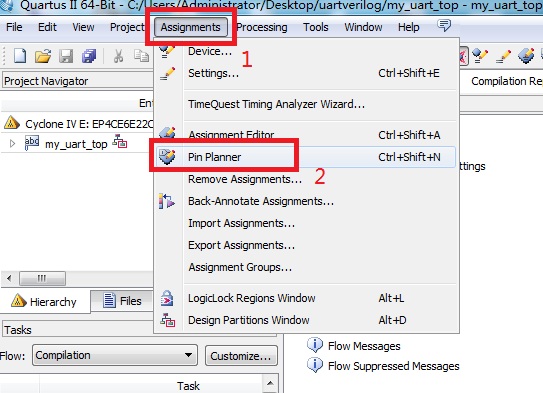

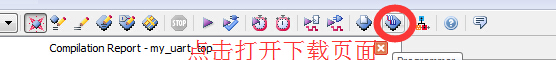

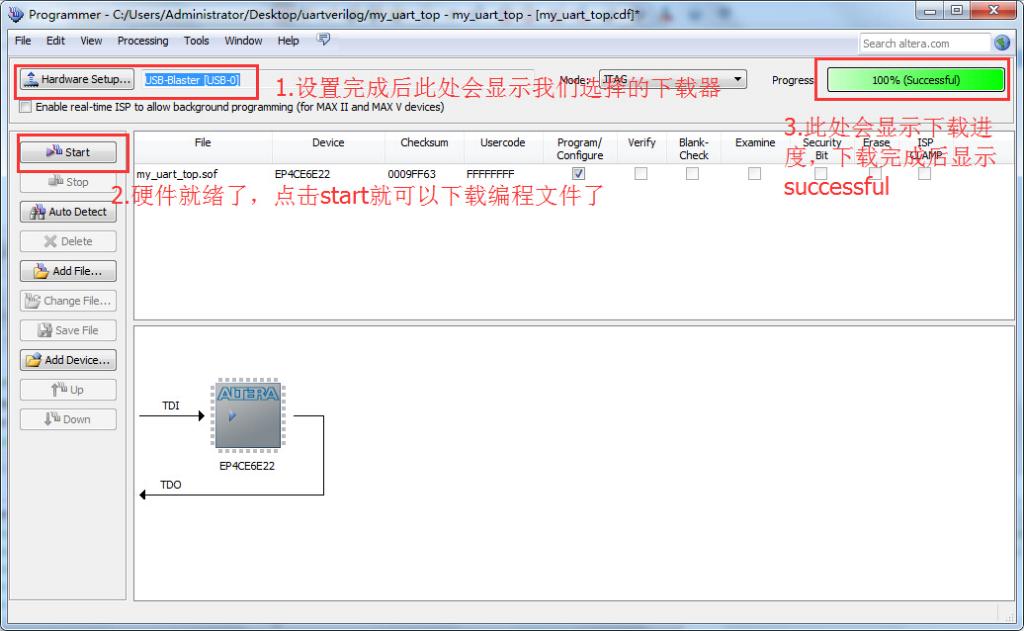

通過以上步驟,我們就實現了PL2303型USB轉串口芯片驅動的安裝。接下來,我們需要根據各自使用的開發板的電路分配引腳,這里小梅哥先用圖文的形式介紹一下針對ZX2開發板的引腳分配及最終將配置文件下載到開發板的流程:

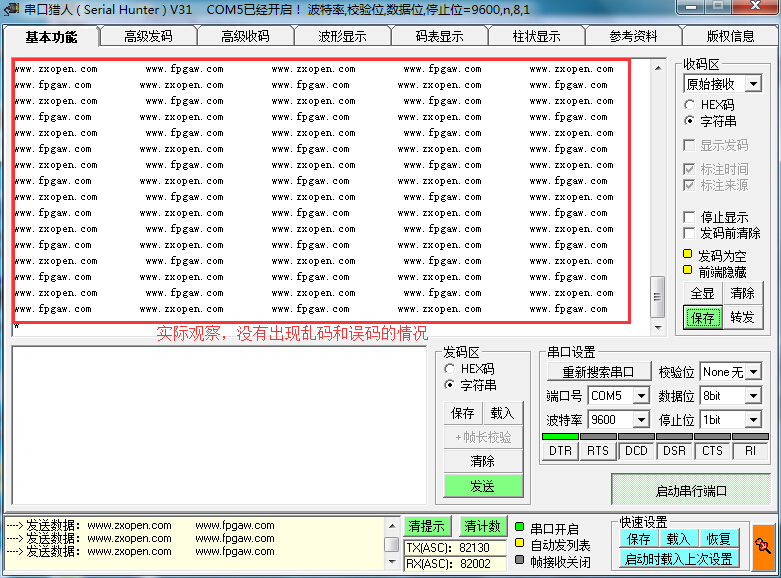

通過以上步驟,電路就已經成功的配置到了我們的開發板上并運行起來了,這個時候,我們就需要通過調試軟件來進行調試,以驗證我們修改后的UART收發模塊能否穩定運行。要調試我們的設計,我們還需要一個串口調試工具,通過串口調試工具,對我們編寫的串口模塊持續發送數據,然后接收串口模塊發送回來的數據,通過對比發送與接收的數據,如果相同,則表明我們的模塊是能夠穩定工作的,如果出現丟碼或者亂碼,表明收發過程中出現了錯誤,則表明我們設計的模塊存在工作不穩定的情況,需要進一步修改優化。

這里,我們使用程序匠人前輩編寫的強大串口調試軟件——串口獵人。該軟件的下載和安裝小梅哥就不多說了,當我們啟動串口獵人軟件后,會顯示以下界面,接下來小梅哥就直接以圖片配文字的形式來一步一步演示該軟件的使用:

通過以上測試,我們知道了,經過小梅哥的修改,該串口模塊目前能夠以連續無間隔的發碼速度進行收發,而且不存在任何誤碼和丟碼。因此,可以說,小梅哥的修改是成功的。

這一篇,主要帶領大家一起進行了串口代碼的分析、仿真模型的設計(testbench)、Quartus II軟件下使用Nativelink調用Modelsim-altera軟件進行仿真、仿真結果簡單分析、串口代碼的修改、串口模塊的板級驗證。相信通過此文,初學者能夠學到部分知識。

這是該系列文檔的第一篇,主要對特權大神的UART代碼進行了簡單的修改,以適應小梅哥自己的用途。下一篇,小梅哥將詳細介紹基于此模塊的擴展設計,其實擴展也沒多少內容,主要就是加上可變波特率功能,順便介紹一下代碼中一些增加設計靈活性的技巧。第三篇,則是小梅哥開始手把手教大家從原理入手,設計我們自己的UART模塊,設計中會加入收發FIFO,并使用標準的Avalon ST接口協議,以形成IP核的形式。

評論