小梅哥和你一起深入學習FPGA之串口調試(一)(下)

以上為小梅哥為了對特權同學的串口收發模塊進行測試所展開的部分工作,到這里,仿真測試所需要的準備工作我們就做好了,接下來將實際進行仿真,通過仿真來分析該模塊的性能。

本文引用地址:http://www.104case.com/article/283060.htm這里極力推薦大家使用modelsim進行仿真,因為quartusII自帶的仿真工具靈活性和功能都趕modelsim相差甚遠。Modelsim作為一款強大的仿真軟件,在業界被廣泛使用。同時,modelsim針對不同的EDA廠家,也推出了OEM版本,modelsim-altera就是為Altera公司開發的OEM版本,此版本針對Altera公司的器件預先做了許多的工作,使我們使用的時候能夠更加的快捷方便,這里,小梅哥就使用modelsim-Altera版本來仿真這個設計。

我們可以使用modelsim-Altera,通過完全手動化的方式來建立仿真工程,添加仿真庫、編譯文件,添加波形,運行仿真,當然也可以使用Nativelink的方式,通過quartus II軟件實現一鍵調用,實現自動化的仿真過程。這里,對于初學者,小梅哥還是推薦采用這種自動化的方式,因為簡單,不需要過多的手動操作,且不容易出錯。這里,小梅哥也使用這種方式來進行仿真。

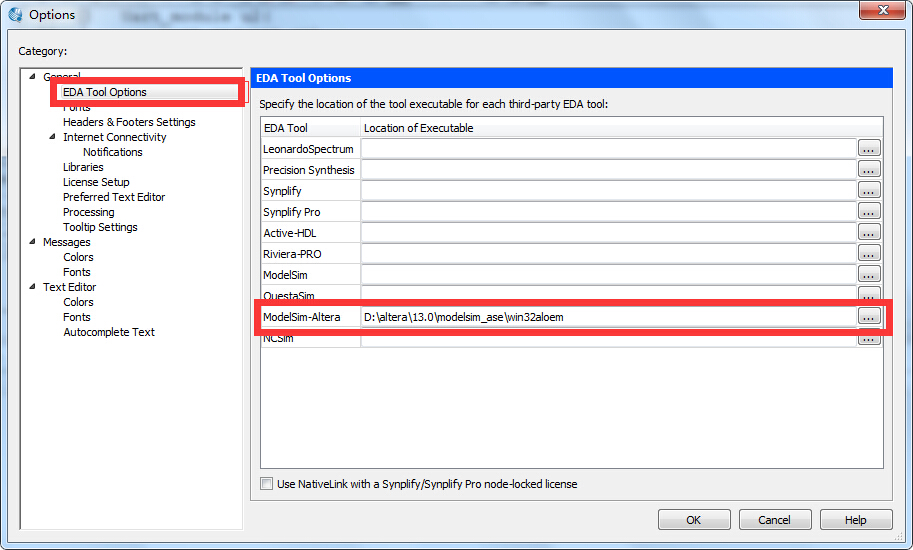

要使用這種方式仿真,我們需要在QuartusII軟件中進行EDA Tools的設置。在quartus II軟件中,依次點擊“tools – options ”,在打開的選項卡中選擇“EDA tool options”,在modelsim-altera一欄中輸入你的modelsim-Altera的安裝路徑(部分在安裝的時候就已經自動設置好了,就不用去管),如下圖所示:

這里設置完成后,點擊OK即可。

當確認這一步沒有問題后,我們就可以開始進行Nativelink的設置了。Nativelive就是一個鏈接的過程,通過設置Nativelink,讓Quartus II軟件能夠自動的調用modelsim-altera軟件,并建立仿真工程,添加仿真庫、編譯文件,添加波形,運行仿真。接下來我們就來進行Nativelink的設置

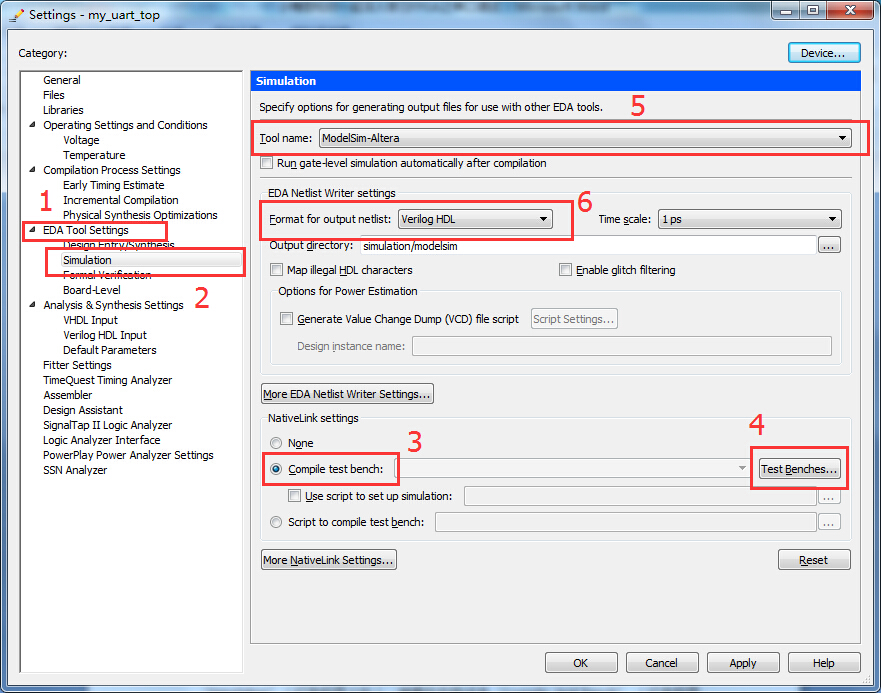

第一步:依次點擊“assignments– settings”,

在彈出的選項卡中,選中“EDA Tool Settings”(紅色標號1處),在子選項中選擇“Simulation”(紅色標號2處),注意紅色標號5處和6處應分別選擇為modelsim-altera和Verilog HDL,如果不是,請通過下拉列表選擇為上述選項。點擊“Compile test bench” (紅色標號3處),然后點擊最右側的“Test Benchs” (紅色標號4處),就會彈出如下所示的界面:

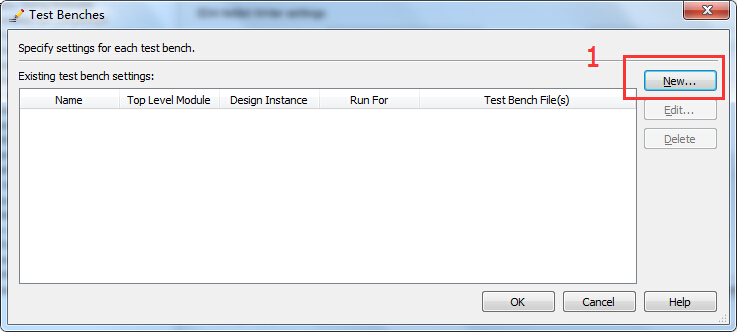

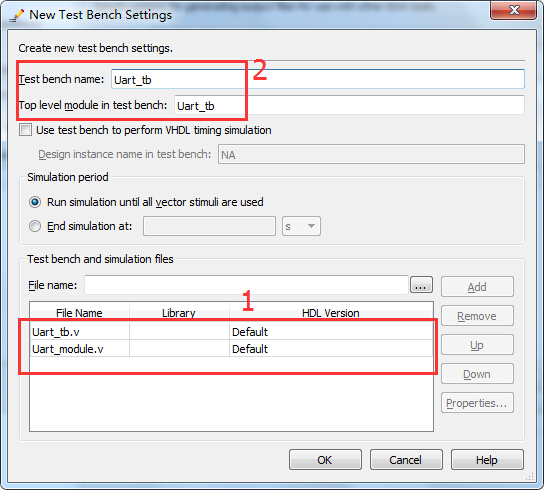

點擊“New” (紅色標號1處),接著會彈出“New Test Bench Settings”界面,如下圖所示:

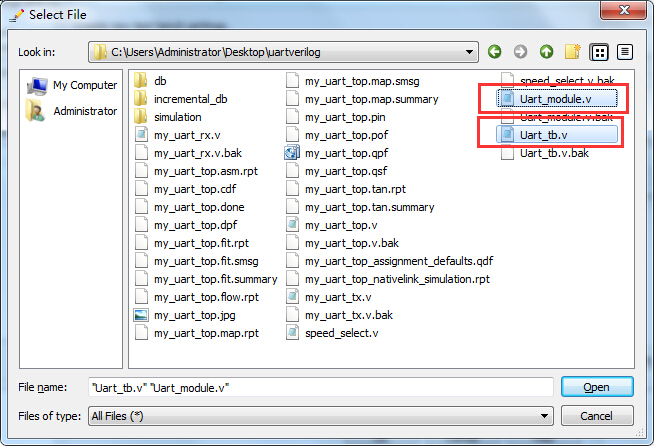

首先我們點擊紅色標號1處的三個小點,在彈出的文件選擇界面中,選中我們需要加入的testbench文件,如下所示:

這里我們選擇“Uart_tb.v”和“Uart_module.v”,點擊“Open”打開。這里,“Uart_tb.v”為仿真頂層文件,“Uart_module.v”為串口仿真模型。

文件選擇好之后,回到New Test Bench Settings界面,如下圖所示,

在頂端“test bench name”(紅色標號2)處輸入我們的仿真頂層文件名,即Uart_tb,注意,不要加“.v”后綴。于是,”Top level module in test bench”會自動與“Test bench name”保持一致。

至此,我們的Nativelink設置就完成了,一路選擇OK下去,直到回到Quartus II軟件的主界面。此時,我們已經完成了仿真需要的所有設置,我們直接點擊Quartus II軟件上的RTL Simulation圖標

即可啟動仿真,也可以通過“Tools– Run Simulation Tool – RTL Simulation”啟動仿真。

接下來,我們需要做的就是大約20秒左右的等待,這個過程中,Quartus II會自動啟動modelsim-altera軟件,建立仿真工程,添加仿真庫、編譯文件,添加波形,運行仿真。最后停留在如下所示的狀態:

這里,右側深色窗口為波形窗口,下方為副本界面,打印了軟件運行過程中的信息,包括添加文件、編譯文件、添加波形、運行等,同時還打印了testbench中需要打印輸出的信息。具體的打印信息如下:

由此打印信息可知,串口仿真模型總共進行了8次數據發送,卻只收到了6次數據,因此有兩次發送給串口模塊的數據丟失或者串口模塊發送的數據不正確。同時,第一次發送出去的數據接收回來還是正確的,但是第二次發送的數據再接收回來,就錯誤了。這兩次數據發送之間的時間間隔為40ns。考慮可能是發送間隔太短導致,但是當第4次發送的數據(s4)被正確接收后(r3),緊接著第5次發送的數據在發回的時候,再次出錯,而s4和s5之間間隔了300ns,因此可知,該串口收發模塊在連續兩次發送間隔很短的情況下,很容易出錯。那么,怎么樣才能保證連續兩次發送之間,即使很短的間隔,也不出錯誤呢?小梅哥通過對仿真波形的分析發現:一次接收數據,總共有12個波特率脈沖,如下圖所示:

這里小梅哥就有點疑惑了,我們一般的應用中,串口一幀的數據為十位,包含1位起始位、8位數據位、一位停止位,一般不含校驗位。因此,這里明顯多了兩個波特率周期,那么,問題很有可能就出在這里。回到這部分的代碼:

43 always @ ( posedge clk or negedge rst_n )

44 if(! rst_n ) begin

45 bps_start_r <= 1'bz ;

46 rx_int <= 1'b0 ;

47 end

48 else if( neg_rs232_rx ) begin

// rs232_rx

49 bps_start_r <= 1'b1 ; //

50 rx_int <= 1'b1 ; //

51 end

52 else if( num==4'd12 ) begin //

53 bps_start_r <= 1'b0 ; //

54 rx_int <= 1'b0 ; //

55 end

56

57 assign bps_start = bps_start_r ;

58

59//---------------------------------------------------------

60 reg[ 7 : 0] rx_data_r ; //

61 //---------------------------------------------------------

62

63 reg[ 7 : 0] rx_temp_data ; //

64

65 always @ ( posedge clk or negedge rst_n )

66 if(! rst_n ) begin

67 rx_temp_data <= 8'd0 ;

68 num <= 4'd0 ;

69 rx_data_r <= 8'd0 ;

70 end

71 else if( rx_int ) begin //

72 if( clk_bps ) begin

// , 8bit 1 2

73 num <= num+1'b1 ;

74 case ( num)

75 4'd1:rx_temp_data[0] <= rs232_rx; // 0bit

76 4'd2:rx_temp_data [1] <= rs232_rx; // 1bit

77 4'd3:rx_temp_data [2] <= rs232_rx; // 2bit

78 4'd4:rx_temp_data [3] <= rs232_rx; // 3bit

79 4'd5:rx_temp_data [4] <= rs232_rx; // 4bit

80 4'd6:rx_temp_data [5] <= rs232_rx; // 5bit

81 4'd7:rx_temp_data [6] <= rs232_rx; // 6bit

82 4'd8:rx_temp_data [7] <= rs232_rx; // 7bit

83 default : ;

84 endcase

85 end

86 else if( num == 4'd12 ) begin//我們的標準接收模式下只有1+8+1(2)=11bit的有效數據

87 num <= 4'd0 ; // STOP ,num

88 rx_data_r <= rx_temp_data ; // rx_data

89 end

90 end

評論