如何實現軟件定義無線電動態范圍的最大化

在為接收器設計設置級聯噪聲系數和截距模型時,您實際上需要為系統建模三次: 一次針對最小信號電平,即最大增益下的AGC關閉電平;第二次針對最大信號電平,即最大增益衰減下的AGC開啟電平;最后一次針對接收器的標稱輸入電平。 您還需要在所有三種模型中考慮交調效應。 幸運的是,ADI的ADISIMRF(圖1)等免費工具將助您一臂之力;這類工具通常內置適用于RF增益塊、混頻器、衰減器、巴倫、濾波器和高速轉換器的模型庫。

本文引用地址:http://www.104case.com/article/279224.htm

頻率規劃是另一項需要廣泛研究的有趣課題。 您不僅需要為每個混頻器(圖2)制作一個混頻器表,而且可能還希望為發射路徑制作一個類似的DAC表。 此外,您還需要考慮在哪個奈奎斯特頻率區域使用轉換器(ADC或DAC)。 系統時鐘通常是幀速率的倍數(這就是1.2288 MHz和13 MHz的倍數之所以常見的原因)。 幸運的是,您可以使用足夠高的頻率(諧波不在頻帶范圍內或目標信號上)。 您需要通過精心挑選系統時鐘、中頻和本振(LO)頻率來最大程度地減少內外部干擾,因為這些頻率將與無法預見的后果混合。

針對級數和功能類型(濾波器、混頻器、放大器等)設置了級聯噪聲系數和截距模型后,就需要執行一些端計算。

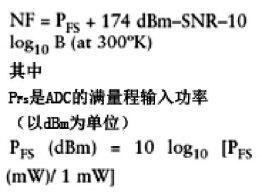

例如,您首先需要使用以下等式計算ADC的噪聲系數(NF):

NR是ADC的信噪比(以dB為單位) ,以及 B是要進行數字轉換的帶寬,需要考慮輸入濾波器的噪聲帶寬(圖3)。

請注意,如果您希望將所需信號加上干擾信號進行數字轉換以濾除數字域中的干擾信號,此帶寬可能比信號帶寬更寬。

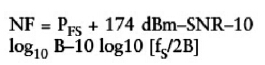

幸運的是,您可以通過對輸入信號過采樣來提高ADC的噪聲系數。在這種情況下,計算噪聲系數的等式將變為:

其中,fS是采樣時鐘,B仍然是信號帶寬(或要進行數字處理的帶寬)。 一些IF采樣ADC(如AD9874和AD9864)會在帶通Σ-Δ架構中使用過采樣和噪聲整形。 這些ADC實際上是完整的IF子系統,接受IF輸入并提供接近100 dB的SNR,以及在輸出時抽取的16或24位I和Q數據。

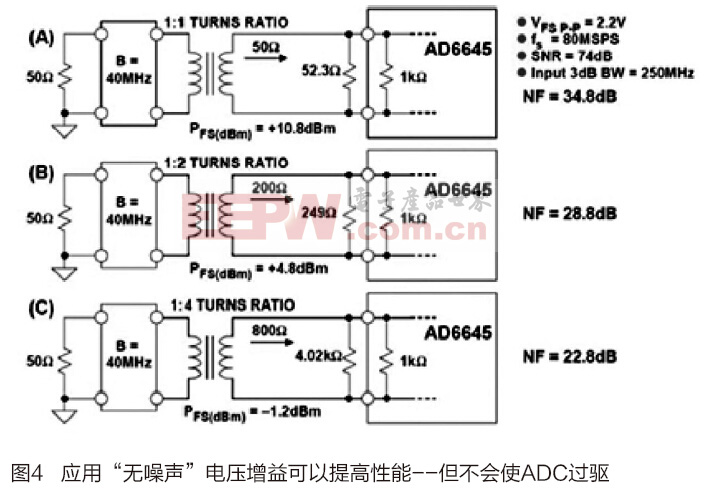

過采樣并不是改善ADC噪聲系數的唯一途徑。您也可以使用變壓器在“無噪聲”增益下提高ADC的輸入電壓,如圖4所示AD6645。

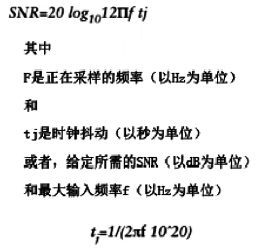

您需要完成的最后一個端計算是針對轉換時鐘的。具有(或缺乏)生成低抖動時鐘的能力是針對高動態范圍的接收器未在天線中放置ADC的原因所在,我們將在下面對此進行介紹。 計算ADC理論上的SNR(作為時鐘抖動的函數)的等式為:

例如,在進行IF采樣時,如果您希望在IF為240 MHz時對20 MHz寬的信號采樣,則頻率最高的采樣元件將是IF加上信號帶寬的一半(或250 MHz)。SNR為80 dB,最大輸入頻率為250 MHz時,可通過求解得出最大時鐘抖動為63.66 fs。您可以仿真PLL/VCO的性能,并使用以下網址提供的ADISIMPLL和ADISIMCLK等免費工具計算各類環路濾波器以及電路配置的抖動:www.analog.com。 借助這些工具,您可以優化環路濾波器的設計以獲得最佳相位噪聲,進而最大程度地減少抖動,這種做法的代價是會增加濾波器的建立時間,但這對高速ADC的固定頻率時鐘來說通常不是問題。

模擬信號相關文章:什么是模擬信號

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

漏電開關相關文章:漏電開關原理

評論