微帶線和帶狀線設計

這里的所有維度同樣以mil為單位,B為兩個層的間距。在這種對稱幾何圖形中,需要注意的是,B同樣等于2H + T。參考文獻2指出,參考文獻1中的這個等式的精度通常在6%左右。

本文引用地址:http://www.104case.com/article/274270.htm適用于εr= 4.0的對稱帶狀線的另一條便利準則是,使B成為W的倍數,范圍為2至2.2。結果將得到約50Ω的帶狀線阻抗。當然,這條法則是以另一近似法為基礎的,忽略了T。盡管如此,該法則對于粗略估算還是很有用的。

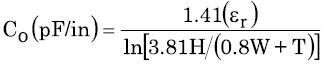

對稱帶狀線同樣有一個特性電容,其計算單位為pF/in,如等式8所示。

對稱帶狀線的傳播延遲如等式9所示。

或者以ps為單位:

當PCB介電常數為4.0時,可以發現,對稱帶狀線的延遲常數幾乎正好為2 ns/ft,合170 ps/in。

走線嵌入法的利弊

根據上述討論,在設計阻抗既定的PCB走線時,既可以置于一個表層之上,也可嵌入兩層之間。當然,在這些阻抗因素之外,還有許多其他考慮因素。

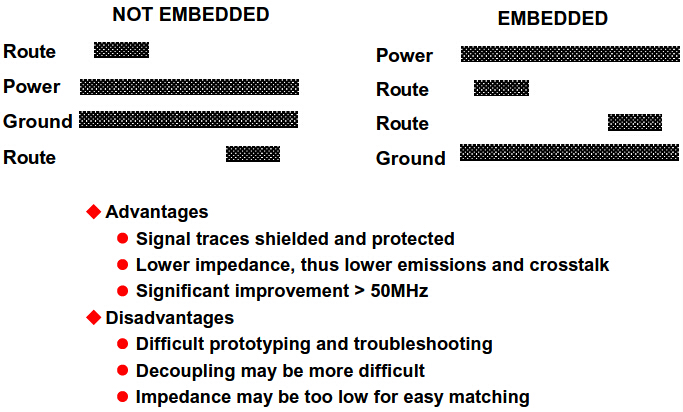

嵌入式信號確實存在一個明顯的大問題——隱藏電路走線的調試非常困難,甚至無法做到。圖4總結了嵌入式信號走線的利弊。

圖4:多層PCB設計中嵌入與不嵌入信號走線的利弊

設計多層PCB時也可能不使用嵌入式走線,如最左邊的橫截面視圖所示。可以將這種嵌入式設計看作一種雙重雙層PCB設計(共有四層銅)。頂部的走線與電源層 構成微帶,底部的走線則與接地層構成微帶。在本例中,兩個外層的信號走線可以方便地供測量和故障排查使用。但這種設計并未利用各層的屏蔽作用。

這種非嵌入式設計的輻射量較大,更容易受到外部信號的影響,而右側的嵌入式設計采用了嵌入法,則很好地利用了各層的優勢。就如諸多其他工程設計一樣,PCB設計中到底采用嵌入法還是非嵌入法是折衷的結果。這里的折衷則體現在減少輻射與方便測試之間。

評論