微帶線和帶狀線設計

作為包括這些計算的示例,一塊雙層板可能用20 mil寬(W)、1盎司(T=1.4)的銅走線,并由10 mil (H) FR-4 (εr= 4.0)的介電材料分離。結果,該微帶線的阻抗為50 Ω左右。對于其他標準阻抗(如75Ω的視頻標準阻抗),使"W"調整為8.3 mil左右即可。

本文引用地址:http://www.104case.com/article/274270.htm微帶線設計的一些指導原則

本例涉及到一個有趣且微妙的要點。參考文獻2討論了與微帶PCB阻抗相關的有用指導原則。若介電常數為4.0 (FR-4),結果顯示,當W/H為2/1時,阻抗將接近50Ω(與第一個示例類似,其中,W = 20 mil)。

仔細的讀者會發現,根據等式3預測,Zo應為46Ω左右,與參考文獻2提到的精度(>5%)相吻合。IPC微帶線等式在50Ω與100 Ω之間最精確,但當阻抗低于或超過該范圍時,其精度則大幅下降。

根據等式5,也可以計算微帶線的傳播延遲。這是微帶信號走線的單向通過時間。有趣的是,對于給定的幾何模型,延遲常數(單位:ns/ft)僅為介電常數而非走線維度的函數(見參考文獻6)。請注意,這可以帶來極大的便利。意味著,當給定PCB基板(并給定εr)時,各種阻抗線路的傳播延遲常數是固定不變的。

該延遲常數也可以ps/in為單位,這樣更適用于小型PCB。即:

因此,舉例來說,對于PCB介電常數4.0,不難發現微帶線的延遲常數約為1.63 ns/ft,合136 ps/in。這兩條額外的準則對于設計PCB走線中信號的時序具有參考意義。

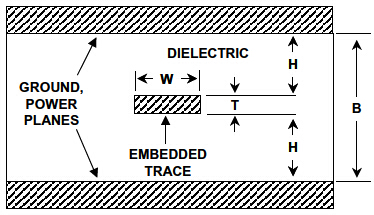

對稱帶狀線PCB傳輸線路

從多種角度來看,多層PCB是一種更好的PCB設計方法。在這種模式下,信號走線嵌入電源層與接地層之間,如圖3中的橫截面視圖所示。低阻抗交流接地層和嵌入的信號走線形成一條對稱帶狀線傳輸線路。

從圖中可以看出,高頻信號走線的電流回路直接位于接地層/電源層上的信號走線的上方和下方。因此,高頻信號被完全限制在PCB板內部,結果使放射降至最低,為輸入雜散信號提供了天然的屏障。

Figure 3: A Symmetric Stripline Transmission Line With Defined Impedance is Formed by a PCB Trace of Appropriate Geometry Embedded Between Equally Spaced Ground and/or Power Planes

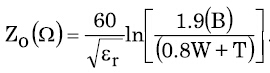

該設計的特性阻抗同樣取決于幾何圖形以及PCB介電質的εr。該帶狀傳輸線路的ZO可表示為:

評論