千兆采樣ADC確保直接RF變頻

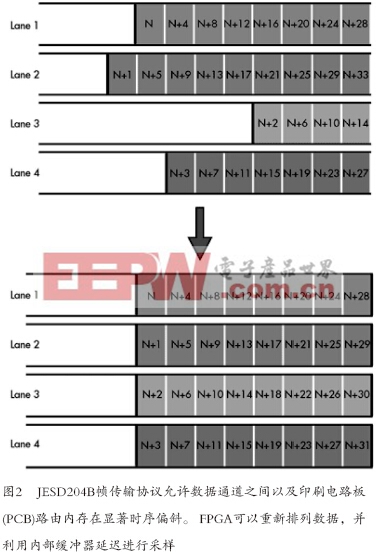

JESD204B提供了一種通過較少數據通道高速輸出數據的方法,且不會出現許多高速LVDS通道面臨的匹配時序電路板復雜度問題。由于通過JESD204B發送的數據是經過基于嵌入式時鐘和控制字符進行幀傳輸的,對較少的串行通道數進行路由時,相比LVDS所需的時序偏斜要求寬松得多(圖2)。因此,無需花費大量時間調整系統PCB上每一個I/O的輸出時序。

此外,JESD204B提供輔助數據的說明性“控制位”,可附加到每一個模擬樣本后,幫助對下游處理進行特征化。通過這種方式,可對每一個樣本標記觸發時間戳和超范圍條件,以便后端FPGA獲得更多數據對齊及有效性信息。

3 超范圍檢測

調整模擬輸入信號的幅度時,自適應增益算法很重要,因為飽和ADC輸入實際上使系統無力解讀信號。理想情況下,增益適應反饋環路應當盡可能快。無論高速ADC輸出是基于LVDS還是采用JESD204B,此數字輸出引入的延遲常常會因為等待時間過長而無法接收飽和數據、檢測問題以及響應條件。

針對這個問題,一種解決方案是在ADC內核中使用可變電平比較,并在發生超范圍條件時直接發送一個即時輸出標志。這種技術避免了較長的后端輸出級延遲,縮短了放大器的反饋時間,實現了更快的自適應增益周期。除了這一“快速超范圍檢測”輸出,可使用JESD204B接口在超范圍樣本上附加報警位,讓下游系統處理就數據作出適當決策。

4 調諧、濾波和抽取:如何處理數據

寬帶ADC具有寬帶采樣的優勢,但也可能會提供超過某些應用需要的數據。對于無需觀察大頻譜的高采樣速率系統,數字下變頻(DDC)允許采用子采樣和濾波策略,以便抽取從GSPS ADC輸出的數據量。然后,下游處理便可觀察到頻譜的較小部分。

在信號鏈上,通常將DDC部署于ADC之后。這不僅會消耗更多的FPGA資源,還要求在ADC和FPGA之間以全帶寬進行傳輸。 DDC濾波可在ADC內部完成,無需將采樣數據發送到FPGA進行處理,因此僅需總帶寬的八分之一或十六分之一。

配合頻率合成數控振蕩器(NCO)使用時,可采用精確的分辨率調諧轉換器DDC濾波器在帶內的準確位置。這樣可支持較低的輸出速率,無需移動或處理FGPA中的大量干擾數據。提供兩個DDC時,每一個DDC都有唯一的NCO,它們可以在頻譜范圍內進行交替步進,以掃描預期信號而不丟失可見性。這在某些雷達應用中很常見。

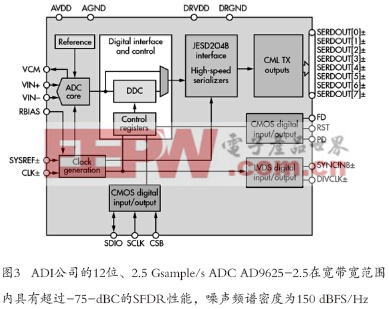

ADI公司的12位、2.5G sample/s ADC AD9625-2.5在寬帶寬范圍內具有超過–75-dBC的SFDR,噪聲頻譜密度為150 dBFS/Hz(圖3)。ADI的專有技術可實現該性能而不產生采樣速率超過1.5 Gsamples/s的千兆赫ADC中常見的交織偽像。集成寬帶頻率調諧器的可選雙通道抽取下變頻濾波器路徑可觀察全頻譜帶寬的八分之一或十六分之一,且每一條路徑都有獨立的10位NCO放置分辨率。

AD9625使用最多八條JESD204B輸出接口通道,因而放寬了LVDS對中常見的匹配走線路由所面臨的布線挑戰。此外,設計人員還可充分利用JESD204B的優勢,比如低引腳數輸出、諧波幀時鐘、每個樣本的控制位信息,以及確定性延遲。

模數轉換器相關文章:模數轉換器工作原理

評論