利用FPGA和分解器數字轉換器簡化角度測量

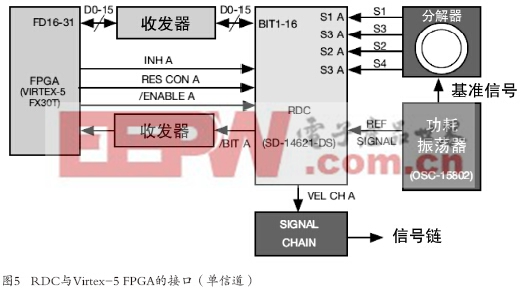

在本設計中采用賽靈思Virtex®-5 FX30T FPGA 。FPGA的I/O電壓為3.3V,而RDC的電壓為5V。因此我們采用電壓收發(fā)器來實現這兩個器件之間的電壓兼容。通過賽靈思提供的GPIO IP核與FPGA建立內部連接,如圖5所示。為了簡單起見,圖5僅顯示一條具有一個分解器接口的信道。

6 器件驅動程序詳細說明

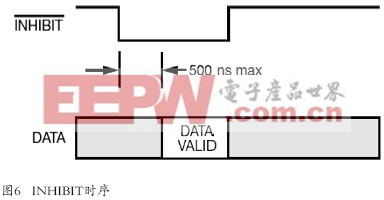

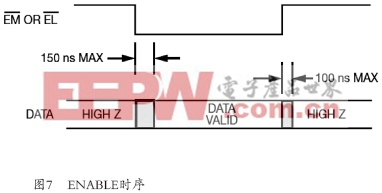

在本例中,FPGA采用20MHz的外部輸入時鐘。此FPGA具有一個運行頻率為200MHz的PowerPC 440硬核。RDC的時序圖見圖6與圖7。

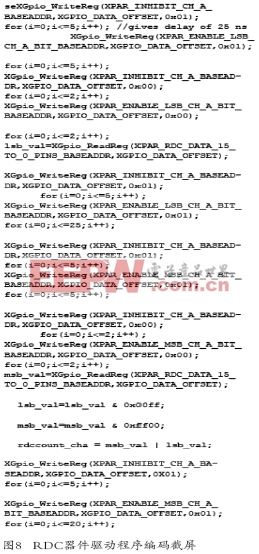

根據RDC的時序圖,我們開發(fā)、測試并驗證了實際硬件的功能是否正確。器件驅動程序的實際編碼包含在單獨的XBD文件中。根據時序圖,我們生成了用于回路的所需延遲。在200MHz運行速率下進行處理時,每個計數都對應5納秒的延遲。

器件驅動程序有三部分編碼:RDC初始化、控制信號的生成及從RDC信道A的讀取、以及控制信號的生成及從RDC信道B的讀取。RDC初始化是設置信號方向和缺省值的階段。例如,利用以下語句,信號方向將設置為從FPGA“輸出”到RDC。

XGpio_WriteReg(XPAR_RESOLUTION_CNTRL_CH_A_

BASEADDR,XGPIO_TRI_OFFSET,0x000);

下一個語句通過寫入“0x3”來設置16位分辨率(即:拉高):

XGpio_WriteReg(XPAR_RESOLUTION_CNTRL_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0x03);

圖8為編碼截屏。注:為了簡化,我們僅提供一條信道的編碼。

我們已經看到,角度傳感器可以幫助工程師創(chuàng)造更好的轉輪,進而設計出眾多更高效的機械裝置。分解器是一種尤為有用的角度傳感器,只要能夠與FPGA正確配合和控制,其就能夠幫助工程師打造出無與倫比的機械裝置。

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理 脈沖點火器相關文章:脈沖點火器原理 數字濾波器相關文章:數字濾波器原理

評論