基于FPGA+DDS的正弦信號發生器的設計

2.2相關電路設計

本文引用地址:http://www.104case.com/article/272867.htm2.2.1 D/A轉換電路

位于波形輸出ROM后的D/A單元,是將數字量形式的波形幅值轉換成所要求的合成頻率的模擬量形式信號[4].由于儲存波形的ROM具有10 bit的輸出,所以采用10 bit的DAC將FPGA輸出的數字信號轉換成模擬信號。本系統采用ADI公司的10 bit COMS數模轉換芯片AD5432,AD5432的驅動電壓為3 V~5.5 V,具有50 MHz的串行接口、10 MHz的乘法帶寬、2.5 MS/s的更新速率,采用±10 V的參考輸入,輸出為電流[5].

2.2.2濾波電路

經由DAC的輸出信號實際上是階梯模擬信號,需利用低通濾波器濾除波形的雜波,并進行平滑處理。由于本系統的最高輸出頻率為10 MHz,所以選取的低通濾波器的截止頻率也應為10 MHz.為了減少系統體積,節省設計時間,提高系統的可靠性,本系統選用凌特公司LT6600-10低通濾波器。LT6600-10內集成了一個全差分放大器和一個近似于切比雪夫響應的四階10 MHz低通濾波器,差分增益由兩個外部電阻設置[6],其基本連接方式如圖3所示。

圖3 LT6600-10 的基本連接方式

3實驗仿真與分析

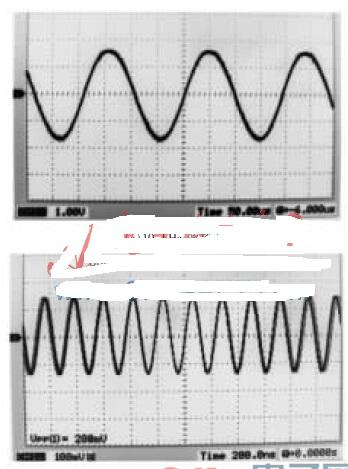

實驗中所用的FPGA芯片為Altera公司的Cyclone III系列,Cyclone III是Altera公司的首款65 nm低成本FPGA,含有5 K~120 K邏輯單元(LE),288個數字信號處理(DSP)乘法器,存儲器達到4 Mbit.Cyclone III系列比前一代產品每邏輯單元成本降低20%,使設計人員能夠更多地在成本敏感的應用中使用FPGA.系統所用的測試頻率(參考頻率)為50 MHz,調試好系統,使系統的輸出從1 kHz~10 MHz遞增,并改變輸出波形的相位,輸出波形的相位變化范圍為0°~360°。經示波器測試,系統的輸出波形形狀良好,輸出波形的實測頻率與理論計算值的絕對誤差小于0.1%,滿足設計要求,有較好的實用價值。圖4為實驗的輸出波形。

圖4 實驗輸出波形

產生測試信號的儀器統稱為信號源,也稱為信號發生器,它用于產生被測電路所需特定參數的電測試信號。信號發生器用途非常廣泛,科學實驗、產品研發、生產維修、IC芯片測試中都能見到它的身影,目前市場上大部分信號發生器多采用DDS頻率直接合成技術。盡管基于FPGA的DDS信號發生器應用廣泛,較傳統的信號源有許多優點,但是由于DDS數字化實現的固有特點,決定了其輸出頻譜雜散較大,又由于DDS內部DAC和ROM的工作速度的限制,使得DDS信號源的最高輸出頻率受限[7].不過,隨著DDS技術的不斷完善和發展,其頻譜雜散、最高輸出頻率的性能指標將得到優化,未來將有越來越多的信號發生器采用DDS技術,所以說對DDS進行研究具有很好的現實意義。

低通濾波器相關文章:低通濾波器原理

負離子發生器相關文章:負離子發生器原理 數字濾波器相關文章:數字濾波器原理 離子色譜儀相關文章:離子色譜儀原理

評論