FPGA電源系統(tǒng)設計能夠采用并行工程嗎?

在開發(fā)過程一開始時,如果設計人員就能夠滿足基于FPGA的設計對電源的要求和約束,這對于系統(tǒng)的最終實現(xiàn)而言是很大的競爭優(yōu)勢。但是,雖然技術文獻在這方面進行了大量的介紹,目前基于FPGA的系統(tǒng)中是否有不實用或者很難實現(xiàn)的東西導致做不到這一點?盡管可以使用各種開發(fā)工具,例如特別針對FPGA工程的早期功耗估算器和功耗分析器等,電源設計人員最好能夠在設計早期階段,考慮電源系統(tǒng)的最差情況,而不是最佳情況,這是因為在硬件設計完成之后,測量功耗之前,動態(tài)負載需求還有很大的不確定性,會在靜態(tài)低電流狀態(tài)和全速工作狀態(tài)之間波動。

本文引用地址:http://www.104case.com/article/271487.htm在當今的設計中,采用并行工程(CE)能否為使用FPGA器件的開發(fā)團隊提供一種方法,在其工程中更方便快速的找到并提取出處理性能、材料表(BOM)成本和能效的最佳平衡點?了解并行工程怎樣影響團隊的設計投入,影響開發(fā)團隊能否在FPGA工程一開始就滿足電源設計要求,以及系統(tǒng)其它部分對電源的要求,這有助于回答這一問題(參考側(cè)邊欄目“并行工程”)。

并行工程這種機制支持設計團隊更迅速的發(fā)現(xiàn)并解決一起工作的各學科之間所做假設的分歧問題,實現(xiàn)最終設計。任何設計團隊都很難在設計一開始時就能夠滿足復雜系統(tǒng)的所有要求——結果,更有效的方法是,盡可能早的發(fā)現(xiàn)、識別并解決所做假設的分歧問題,做出設計決定,以盡可能低的成本,采用與工程所需產(chǎn)出最貼近的設計假設和決定替代以前的假設和決定。

設計后期的情況越來越復雜,最差情況下的FPGA電源系統(tǒng)設計能夠采用并行工程實踐嗎?為回答這一問題,我們需要理解:是什么原因?qū)е翭PGA電源系統(tǒng)設計人員面臨如此復雜而且不確定的設計,設計電源時,要做出哪些取舍?

復雜性和不確定性

設計團隊中的每一名成員都體會到復雜性和不確定性——隨著集成度的提高,以及設計的抽象化,復雜性和不確定性也稍有緩和,設計人員還能夠接受和理解這種復雜性,并進行工作。設計即將結束時,每一學科都會對設計有所貢獻,上游設計假設和決定會導致更加復雜和不確定,如果盡早進行協(xié)調(diào)和溝通,會減輕這方面的影響。

在越來越復雜的系統(tǒng)中,電源設計是下游學科之一。對于這一情形,讓我們從電源設計人員的角度看一下復雜性和不確定性的來源。影響電源設計的兩個關鍵FPGA規(guī)范是電壓和電流要求。

FPGA電壓要求越來越復雜,這是因為所需要的電源軌越來越多了。以前,內(nèi)核和I/O單元需要兩個電源軌,還有可能采用第三個用于其他功能,而現(xiàn)在的高端FPGA會需要數(shù)十個外部驅(qū)動的電源軌。

為什么所需要的電源軌數(shù)量會急劇增長? SRAM單元需要的電壓要比內(nèi)部邏輯門稍高一些,以保證可靠的全速工作,而待機模式的電壓要低一些。工業(yè)標準會鎖定各種I/O單元,以及不同電源的物理接收和發(fā)送接口,這些電源具有不同的供電噪聲限制和電壓電平,因此能夠防止不同的I/O單元共享同一個電源軌,這增加了所需要的電源軌數(shù)量。例如,以太網(wǎng)運行的I/O電壓與I2C總線不同。一個是板上總線,另一個是外部總線,但是都能夠在FPGA中實現(xiàn)。降低敏感電路的抖動或者提高噪聲余量會要求更多的電源軌,例如低噪聲放大器、鎖相環(huán)、收發(fā)器以及高精度模擬電路等,因為即使是工作在同樣的電壓下,它們也無法共享含有噪聲分量的電源軌。

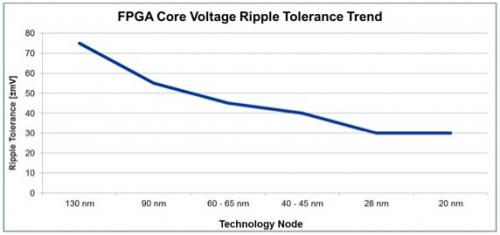

除了需要越來越多的電源軌之外,當今的FPGA工作電壓要低于以前的產(chǎn)品代,這對于降低功耗和提高集成度很重要,但是由于電源必須維持要求越來越嚴格的電壓容限,因此,這也提高了復雜度(參見圖1)。例如,在28 nm技術節(jié)點,公開的FPGA內(nèi)核電壓波紋容限幅度比130 nm制造的FPGA低了一半多。誤差余量百分比從5%降到3%,還會繼續(xù)降到2%.滿足電壓容限要求有助于理解并滿足FPGA電流要求。

圖1.四個技術節(jié)點的平均電壓波紋容限降低了一半多,這對于電源設計人員而言,意味著復雜度提高了。

fpga相關文章:fpga是什么

鎖相環(huán)相關文章:鎖相環(huán)原理 鎖相放大器相關文章:鎖相放大器原理

評論