基于FPGA的高速PID控制器設計與仿真

3 工作控制狀態機的設計

本文引用地址:http://www.104case.com/article/270111.htm典型的數字PID控制系統由A/D轉換、PID控制算法和D/A轉換三個關鍵環節構成。為了協調三個環節之間的工作流程,系統工作控制部件必不 可少。純硬件數字系統的順序控制有多種方案可選,如單片機輔助控制、嵌入式CPU軟核控制、脈沖計數控制等等,但都難以兼顧系統的高速控制和靈活擴展。在 高速運算和控制方面,有限狀態機具有以上幾種控制方式難以超越的優越性。

從狀態機的信號輸出方式上分,有Moore型和Mealy型兩類狀態機。從輸出時序上看,前者屬于同步輸出狀態機,而后者屬于異步輸出狀態機。Mealy型狀態機的輸出是當前狀態和所有輸入信號的函數,它的輸出是在輸入變化后立即發生的,不依賴于時鐘的同步[2]。

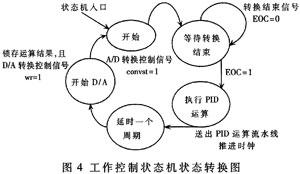

Moore型狀態機的輸出則僅為當前狀態的函數,這類狀態機在輸入發生變化時還必須等待時鐘的到來,時鐘使狀態發生變化時才導致輸出的變化,所 以比Mealy機要多等待一個時鐘周期,但是能有效避免毛刺現象。本設計所用的狀態機為單進程Moore型狀態機。狀態轉換如圖4所示。

4 系統實現與功能仿真

整個PID控制器的系統設計采用自頂向下的設計方法和模塊化的設計思想,即先由PTD控制器的自然語言描述得到VHDL的系統行為描述,然后對系統分解為誤差A/D變換部件、PID運算部件、控制增量D/A變換以及協調三者的控制狀態機等四個主要模塊。

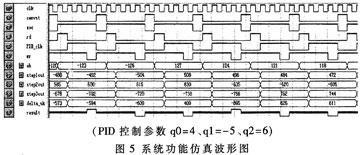

Altera公司專用EDA軟件QuartusII支持原理圖與VHDL語言混合輸入設計方式,除PID運算部件采用原理圖輸入設計方式以外,其余三個部件均采用VHDL輸入設計方式。系統仿真時,如果將系統的最高工作速率設定為120MHz,則采樣速率為24MHz。功能仿真波形圖如圖5所示。

通過對增量式數字PID控制算法的優化處理,顯著提高了系統的工作速度。仿真結果表明,擁有較低轉換速率的A/D變換技術成為提高系統運行速度的瓶頸。就本設計采用的閃爍型A/D器件而言,減少狀態機等待A/D轉換結束信號EOC(見圖4)的時間,即提高A/D轉換的速率是提高系統整體工作速率的關鍵。

本設計中所采用的增量式數字PID控制算法的設計思想可以應用到有限長單位脈沖響應(FIR)濾波器和無限長單位脈沖響應(ⅡR)濾波器的FPGA設計中,并且同樣可以使用流水線優化技術以提高工作速度。同時,由于PLD設計和專用ASIC設計的通用性,在PLD設計平臺上所完成的設計可以很自然地過渡到專用ASIC的設計工作中,進一步提高了系統的可靠性和集成度。

pid控制相關文章:pid控制原理

fpga相關文章:fpga是什么

伺服電機相關文章:伺服電機工作原理

pid控制器相關文章:pid控制器原理

評論