基于FPGA的跨時鐘域信號處理——借助存儲器

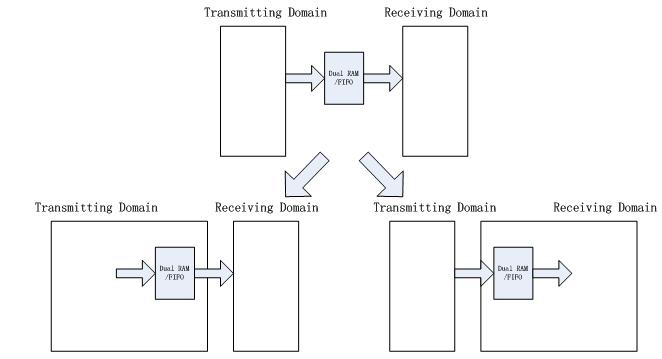

為了達到可靠的數據傳輸,借助存儲器來完成跨時鐘域通信也是很常用的手段。在早期的跨時鐘域設計中,在兩個處理器間添加一個雙口RAM或者FIFO來完成相互間的數據交換是很常見的做法。如今的FPGA大都集成了一些用戶可靈活配置的存儲塊,因此,使用開發商提供的免費IP核可以很方便的嵌入一些常用的存儲器來完成跨時鐘域數據傳輸的任務。使用內嵌存儲器和使用外部擴展存儲器的基本原理是一樣的,如圖1所示。

本文引用地址:http://www.104case.com/article/270067.htm

圖1 借助存儲器的跨時鐘域傳輸

雙口RAM更適合于需要互通信的設計,只要雙方對地址做好適當的分配,那么剩下的工作只是控制好存儲器的讀寫時序。FIFO本身的特性(先進先出)決定了它更適合于單向的數據傳輸。總之,借助存儲器進行跨時鐘域傳輸的最大好處在于,設計者不需要再花時間和精力考慮如何處理同步問題,因為這些工作都交給了存儲器,我們也不用關心存儲器內部到底使用了怎樣的工作機制來解決沖突問題(當然了,存儲芯片內部肯定是有一套完善的同步處理機制)。我們可以把更多的時間花在數據流以及存儲器接口的控制上。借助存儲器的另一個優勢,它可以大大提高通信雙方的數據吞吐率,它不像握手信號和邏輯同步處理機制那樣在同步設計上耗費太多的時鐘周期,它的速度瓶頸基本就是存儲器本身的速度上限。不過,在得到便利的同時,我們也不得不以付出更多的Money作為代價。

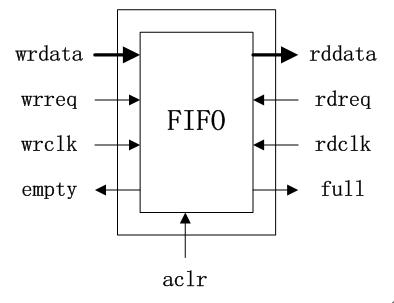

下文將重點探討異步FIFO在跨時鐘域通信中的使用。常見的異步FIFO接口如圖2所示,FIFO兩側會有相對獨立的兩套控制總線。若寫入請求wrreq在寫入時鐘wrclk的上升沿處于有效狀態,那么FIFO將在該時鐘沿將鎖存寫入數據總線wrdata。同理,若讀請求rdreq在讀時鐘rdclk的上升沿處于有效狀態,那么FIFO將把數據放置到讀數據總線rddata上,外部邏輯一般在下一個有效時鐘沿讀取該數據。

FIFO一般還會有指示內部狀態的一些接口信號,如圖2中的空標志位empty、滿標志位full,甚至還會有用多位數據線表示的FIFO當前數據量,這些狀態標志保證了讀寫控制不出現空讀和滿寫的情況。清除信號aclr在某些應用中也是需要的,它在有效時能夠清除當前FIFO的數據,讓FIFO復位到一個空的狀態。

圖2 常見異步FIFO接口

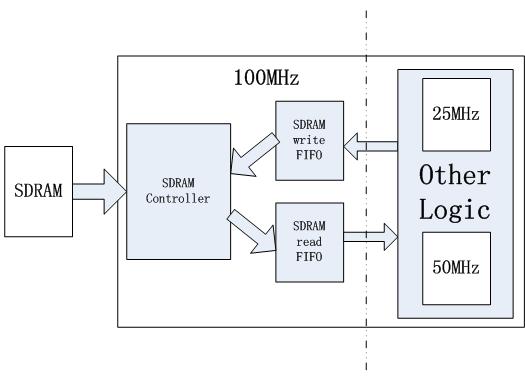

如圖3所示,在特權同學設計過的一個SDRAM控制器中,就使用了兩個FIFO。由于SDRAM需要定時預刷新,并且每次讀寫時起始控制的時間開銷相對大一些,因此采用頁讀寫的方式可以大大的提高數據吞吐量,而頁讀寫方式需要對數據做一些緩存處理。另外,該SDRAM控制器所在的工程中涉及了多個時鐘域。在寫入SDRAM端是一個25MHz的時鐘,在讀SDRAM端是一個50MHz的時鐘,而SDRAM的控制則使用了100MHz的時鐘。盡管實際工程里這三個時鐘的相位關系固定,但是不做好多周期約束也很容易引起問題。

最終,選擇在SDRAM控制器的寫入端和讀出端各使用一個異步FIFO,這既解決了數據緩存的問題,也能有效的完成跨時鐘域的信號傳輸。

圖3 用兩個FIFO設計的SDRAM控制器

樹莓派文章專題:樹莓派是什么?你不知道樹莓派的知識和應用

fpga相關文章:fpga是什么

存儲器相關文章:存儲器原理

評論