降低工業(yè)應用的總體擁有成本

摘要:大約三分之一的嵌入式設計人員考慮在嵌入式應用中采用FPGA,他們認為在設計中使用FPGA過于昂貴。但是,從系統(tǒng)級了解總體擁有成本(TCO) (由產品生命周期中的開發(fā)、改進、替換和維護成本來衡量),您會發(fā)現(xiàn)FPGA是分立微控制器(MCU)/數(shù)字信號處理器(DSP)/ASSP產品靈活的競爭方案。

本文引用地址:http://www.104case.com/article/269811.htm引言

工業(yè)自動化和過程控制生產商一直面臨持續(xù)的全球競爭和經濟壓力,商業(yè)模式和利潤不斷受到威脅,不得不應對成本挑戰(zhàn),包括:

● 利潤和研發(fā)投入;

● 產品及時面市壓力以適應經濟狀況的變化;

● 高效使用有限的資源以更新和替換現(xiàn)有產品,或者發(fā)布新產品;

● 管理產品生命周期。

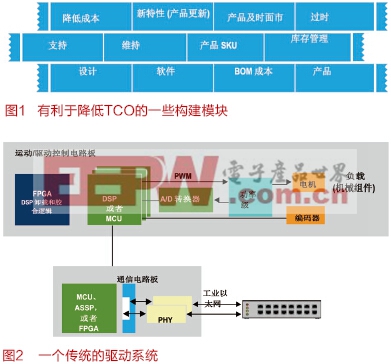

本文使用一個設計實例來幫助包括系統(tǒng)、硬件和軟件工程師在內的設計人員理解怎樣利用Altera Cyclone®和MAX® 10 FPGA來降低總體擁有成本(TCO),它由系統(tǒng)生命周期內的開發(fā)、改進、替換和維護成本來衡量。如圖1所示,較低的TCO直接提高了毛利潤,從而減緩了當今大部分設計團隊所面臨的壓力。

FPGA降低了TCO

為闡述Altera Cyclone和MAX 10 FPGA是怎樣降低TCO的,本文使用驅動控制應用程序(圖2)作為一個實例,用于解決用戶可能面臨的工業(yè)設計難題。MCU和DSP是目前這種運動/驅動控制體系結構的基礎,同時FPGA體系結構發(fā)展很快。MCU/DSP體系結構有很好的用戶基礎,其成熟的體系結構、開發(fā)工具以及運動控制算法主要用于單軸驅動應用中。驅動系統(tǒng)越來越復雜,驅動控制軸數(shù)量也越來越多,產品功能在增加,MCU/DSP體系結構在性能上很快便不能滿足要求,無法靈活地應對市場需求的變化。隨著系統(tǒng)性能的提高,設計人員只能提高MCU/DSP頻率,優(yōu)化某一點的軟件算法。

為解決這一問題,設計人員使用多個DSP器件,結合DSP和MCU器件,或者同時使用MCU/DSP器件以及FPGA來劃分其設計的性能和功能。雖然MCU/DSP體系結構能夠在一定程度上重新使用代碼,但是,重新使用經過高度優(yōu)化的代碼會付出很大的勞動,很難進行劃分并將其應用到新器件中。

工業(yè)網(wǎng)絡過渡到基于以太網(wǎng)的網(wǎng)絡,通常需要將驅動系統(tǒng)連接至這些工廠網(wǎng)絡。而MCU和一些較新的數(shù)字信號處理器能夠支持(標準)具有軟件開銷的以太網(wǎng)TCP/IP,這種組合會有問題,原因如下:

● 大部分MCU帶寬不足,大部分數(shù)字信號處理器不能在處理工業(yè)以太網(wǎng)和現(xiàn)場總線協(xié)議的同時完成驅動控制。

● MCU在其PWM輸出上進行精確運動控制的能力有限。

● 很多DSP器件無法滿足TCP/IP堆棧要求,因為其體系結構缺少支持TCP/IP所需要的字對齊功能。

這些難題意味著設計人員不得不使用更多的MCU、ASSP或者FPGA器件以連接目前的產品和工業(yè)網(wǎng)絡。

縮短產品面市時間

使用一個或者多個MCU或者DSP器件實現(xiàn)驅動控制功能,考慮額外的網(wǎng)絡和安全要求,這都會將開發(fā)時間延長18到24個月。額外的時間意味著提高了研發(fā)成本,有可能降低收益和利潤。當電路板上增加額外的元器件時,也會增大產品的BOM成本。

使用現(xiàn)有軟件

軟件工程師可以把他們的MCU/DSP經驗應用到可編程嵌入式CPU上,例如,Altera的雙核ARM Cortex®-A9 MPCore™,Nios II嵌入式處理器,ARM Cortex-M1和Freescale的ColdFire V1內核,這些都可以與Altera FPGA一起使用。

當今電子產品的功能要比10年前強大得多,而且更加靈活和復雜,包括使用處理器、操作系統(tǒng)和應用軟件所實現(xiàn)的功能。很多產品已經發(fā)展到軟件設計上的投入時間要比硬件設計多出很多人工年。這表明,考慮到產品更新,選擇的處理器如果不支持與當今系統(tǒng)相同的操作系統(tǒng),會需要進行大量的軟件導出工作,導致工程在器件選擇和靈活性上受到很大限制。

linux操作系統(tǒng)文章專題:linux操作系統(tǒng)詳解(linux不再難懂)

評論