認知無線電的頻譜檢測的FPGA實現

初步擬定硬件方案

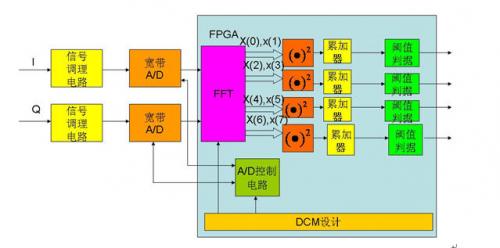

本文引用地址:http://www.104case.com/article/269587.htm(1)整體方案框圖

本次設計使用8點的FFT設計,因此我們需要3級基2點的FFT運算,共有4個旋轉因子需要存儲,依據項目難點我們主要對FFT模塊的設計進行逐層細化:

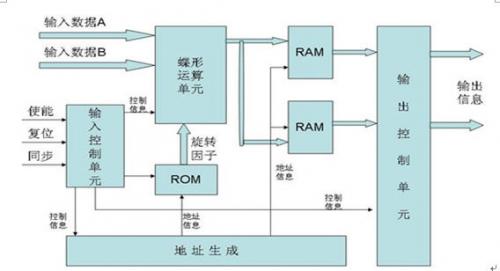

(2)一級FFT的系統框圖實現

該框圖為一級FFT的系統框圖,輸入數據A對應I信號的輸入,輸入數據B對應Q信號的輸入,然后對其做基2點的FFT運算。

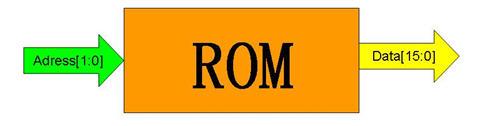

(3)ROM的設計

本次設計為8點FFT運算,就需要4個旋轉因子,旋轉因子的實部和虛部都采用八位二進制數來表示,因此使用一個寬度為16,深度為4的ROM存儲器存儲旋轉因子。

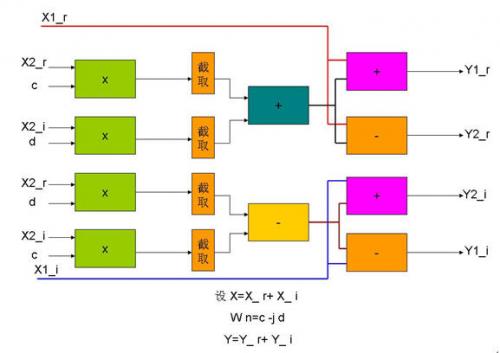

(4)蝶形運算單元的FPGA實現

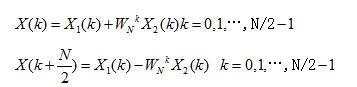

依據蝶形運算公式:

我們得到蝶形運算單元框圖為:

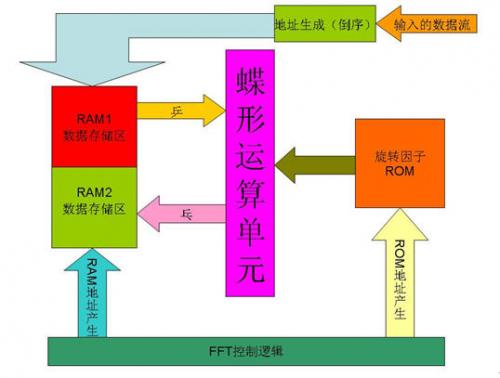

(5)乒乓結構的RAM示意圖

我們在FFT模塊中開辟兩個RAM數據存儲區,以此組成典型的乒乓操作模式;在FFT第一級運算中,數據從RAM1經蝶形運算單元計算存入RAM2,在第二次中則正好相反,以此類推…….,下圖給出了乒乓結構的RAM示意圖。

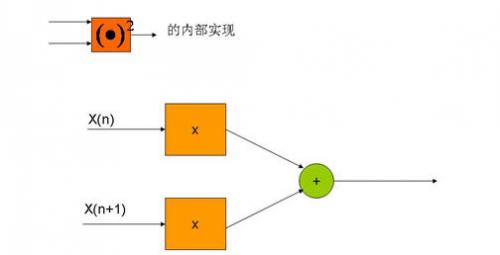

(6)能量求和模塊

最終輸出信號為:y=x(n)*x(n)+x(n+1)*x(n+1);

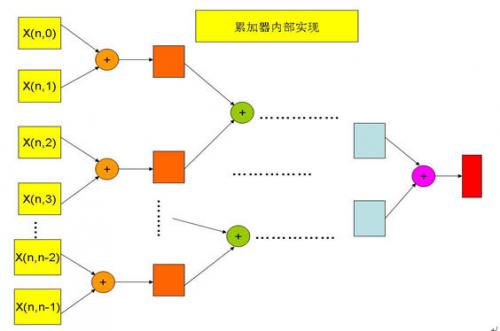

(7)累加電路模塊

我們將能量計算模塊計算出的能量值通入一個長度為n的FIFO結構,每當FIFO結構中有一個數據量發生變化時,累加器都要進行計算更新,這樣就做到了實時監測該通道的頻譜占用情況。在累加器當中,為了計算速度足夠的快,可以滿足實時性要求,我們往往設計為流水線結構。如下圖所示:以流水線結構實現的累加器

fpga相關文章:fpga是什么

評論