FPGA設計開發軟件ISE使用技巧之:典型實例-增量式設計演示

6.9 典型實例12:增量式設計(Incremental Design)演示

本文引用地址:http://www.104case.com/article/269340.htm6.9.1 實例的內容及目標

1.實例的主要內容

6.7節對增量式設計這一方法的基本概念和流程做了全面的介紹。本節將以一個具體的實例幫助讀者熟悉增量式設計的操作流程。

本實例的源代碼參見隨書光盤Example6.9。此程序為PC機通過串口向SRAM寫入數據,再由FPGA從SRAM中讀取數據通過串口將其送到PC機。

本實例的重點在于設計過程中是如何應用增量式設計的,而不是如何實現程序本身的功能。

2.實例目標

通過本訓練,讀者應達到下面的目標。

· 掌握增量式設計與一般設計的區別。

· 掌握增量式設計的設計流程。

6.9.2 實例詳解

增量式設計的具體實現步驟如下。

(1)打開ISE工程。

設計的第一步為創建邏輯分組。

在本設計中,top.v為頂層模塊。頂層模塊中包含兩個功能模塊,分別為:uart_rs232.v和sram.v。uart_rs232.v用于完成串口數據傳輸,sram.v用于對于SRAM的基本讀寫操作。

top.v頂層模塊中,僅包含這兩個模塊,沒有其他復雜邏輯。并且每個邏輯分組均以寄存器輸出,可將這3個模塊看作3個邏輯分組,滿足創建邏輯分組所必須遵循的原則。

(2)綜合。

為了保證在后面的實現中能夠準確地完成分組區域約束,這里需要對綜合的屬性進行設置,在“Processes for Source”中選擇“Synthesize-XST”,單擊鼠標右鍵,設置綜合屬性如圖6.86所示。

圖6.86 設置綜合屬性對話框

選擇“Synthesis Options”/“Keep Hierarchy”,設置綜合屬性為保留結構層次模式。

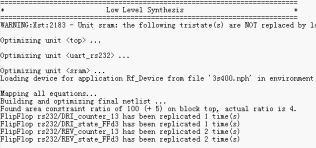

綜合完畢要查看綜合報告,為了和下面流程中的增量綜合結果作對比,請特別注意綜合報告中如圖6.87所示的部分。在沒有進行增量綜合時,要對每個模塊都進行綜合和優化。

圖6.87 未設置綜合約束條件時的綜合報告

(3)設置管腳約束。

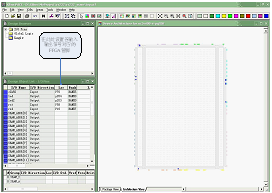

在“Processes for Source”中選擇“Assign Package Pins”啟動設置管腳約束的工具PACE,如圖6.88所示,在Loc處設置各信號對應的FPGA管腳。具體設置可參見例程代碼Source文件夾下的top.ucf文件。

圖6.88 設置管腳約束界面

fpga相關文章:fpga是什么

評論