FPGA設(shè)計(jì)開發(fā)軟件ISE使用技巧之:典型實(shí)例-ChipScope功能演示

(12)生成ILA核。

本文引用地址:http://www.104case.com/article/269339.htm單擊圖6.69中的“Generate Core”按鈕,生成邏輯分析儀(ILA),如圖6.70所示。

圖6.67 設(shè)置觸發(fā)參數(shù)對(duì)話框

圖6.68 設(shè)置存儲(chǔ)深度和數(shù)據(jù)位寬對(duì)話框

圖6.69 設(shè)置生成實(shí)例的語言類型和綜合工具

圖6.70 生成ILA核

(13)將ICON和ILA插入設(shè)計(jì)。

完成上述步驟后就完成了集成控制核(ICON)和邏輯分析儀(ILA)的生成,系統(tǒng)生成的主要文件如表6.5所示。

表6.5 ChipScope生成文件列表

icon.edn集成控制器的網(wǎng)表文件

icon.ncf集成控制器的網(wǎng)表約束文件

icon_xst_example.v集成控制器的嵌入式例子代碼

ila.end集成邏輯分析儀的網(wǎng)表文件

ila.ncf集成邏輯分析儀的網(wǎng)表約束文件

ila_xst_example.v集成邏輯分析儀的嵌入式例子代碼

用戶需要做的是根據(jù)提供的例程代碼來修改自己的代碼,將生成的集成控制核和集成邏輯分析儀插入到設(shè)計(jì)當(dāng)中。具體修改時(shí),需要在源文件中添加如下代碼:

icon i_icon // ICON core instance,實(shí)例化ICON核

(

.control0 (control0)

);

wire [7:0] trig0;

ila i_ila // ILA core instance,實(shí)例化ILA核

(

.control (control0),

.clk (clk),

.trig0 (trig0)

);

assign trig0 = count;

從代碼中可以看出要做的工作主要是實(shí)例化ICON核和ILA核。注意要將觀察的信號(hào)(在這里為count)與ILA核的輸入信號(hào)相連接,系統(tǒng)時(shí)鐘與ILA核的時(shí)鐘輸入相連接,ICON的輸出控制信號(hào)與ILA的輸入控制信號(hào)相連接。這樣就可以通過修改RTL代碼來插入集成邏輯控制器和集成邏輯分析儀了。

(14)綜合,布局布線,生成配置文件并下載。

具體的操作步驟可以參看2.6節(jié)的介紹,這里不再詳述。需要注意的是ChipScope Pro要通過JTAG接口與器件連接。生成配置文件時(shí),時(shí)鐘要設(shè)置為JTAG Clock。

(15)啟動(dòng)ChipScope Pro Analyzer。

可通過直接運(yùn)行“開始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Analyzer”,也可以在ISE集成環(huán)境下,在進(jìn)程瀏覽器中雙擊“Analyze Design Using ChipScope”啟動(dòng)。啟動(dòng)后界面如圖6.71所示。

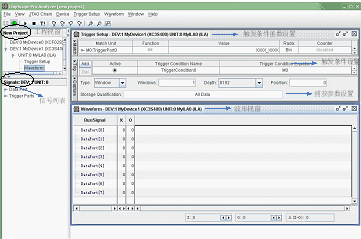

(16)打開JTAG連接。

單擊

(17)設(shè)置觸發(fā)條件。

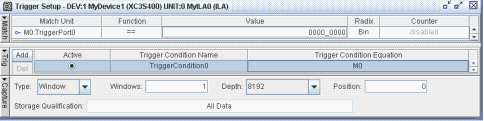

觸發(fā)條件設(shè)置如圖6.73所示。

圖6.71 ChipScope Pro Analyzer用戶界面

圖6.72 成功連接后用戶界面

圖6.73 設(shè)置觸發(fā)條件對(duì)話框

設(shè)置觸發(fā)條件函數(shù)為“==”,數(shù)值為0000_0000(也就是說,觸發(fā)端口的信號(hào)值為0000_0000時(shí)開始采集數(shù)據(jù))。設(shè)置采集深度為8192。這里只有一個(gè)觸發(fā)件M0,只需采用默認(rèn)即可。當(dāng)有多個(gè)條件時(shí),要在“Trig”選項(xiàng)卡下設(shè)置起作用的正確條件,也可將觸發(fā)條件設(shè)置為幾個(gè)條件的邏輯組合。

fpga相關(guān)文章:fpga是什么

塵埃粒子計(jì)數(shù)器相關(guān)文章:塵埃粒子計(jì)數(shù)器原理

評(píng)論