CPLD對FPGA從并快速加載的解決方案

之后CPU通過和CPLD的接口③——8位的局部總線接口,將配置數據逐字節的寫入CPLD的寄存器中。以MIPS系列CPU XLS408為例,XLS408工作時鐘頻率為66.7 MHz,寫總線周期最快需要10個工作時鐘周期,即6.67 MHz,這一步受局部總線速度限制。

本文引用地址:http://www.104case.com/article/268445.htm數據寫入到CPLD后,再通過接口④——CPLD與FPGA之間的從并接口,將數據加載到FPGA,從并接口是同步總線,加載時間受限于總線時鐘CCLK頻率。

本方案的優點為:①、②兩條路徑可以在加載之前處理,且運行速度快,不占用加載時間。加載時間只受③、④的限制,而③受限于寫總線周期間隔,④受限于從并接口的時鐘。

3.2程序實現

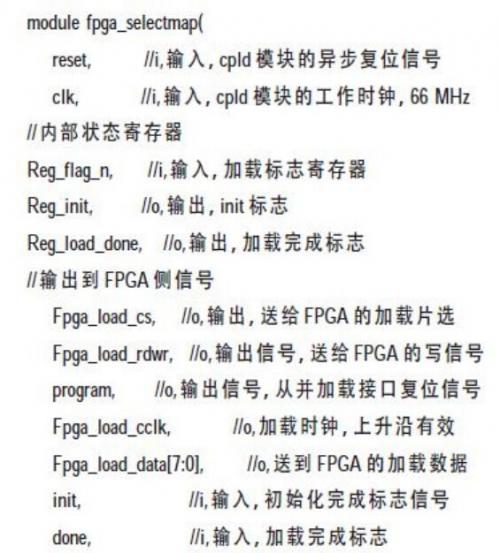

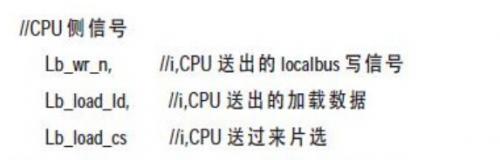

CPLD從并程序采用verilog語言實現,該加載模塊接口定義如下:

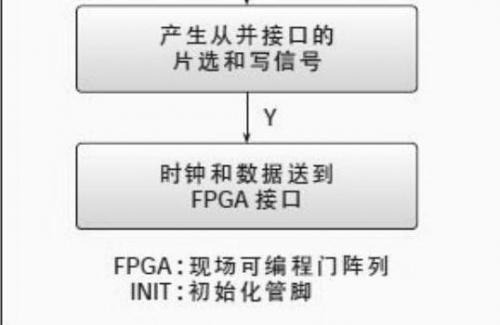

程序實現流如圖3所示。

圖3基于CPLD從并加載FPGA的程序流程

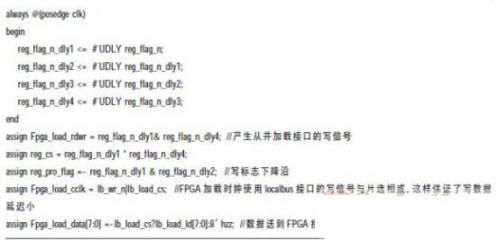

FPGA加載片選和寫信號產生部分代碼如下:

評論