基于FPGA的LCD大屏幕拼接系統的設計

項目概述

本文引用地址:http://www.104case.com/article/266848.htm隨著各種圖形、圖像內容質量的不斷提升以及系統運行實時顯示的需要,金融、通信、交通、能源、安全、軍事等越來越多的行業需要建立能夠實時整合多路信號輸入的超大屏幕顯示系統。而數字技術的飛速發展,也使人們對大尺寸、多畫面、真色彩、高畫質、高分辨率的計算機圖形、圖文、數據與各類視頻圖像顯示效果的需求得以滿足。其中,以視頻信息的要求最為強烈,人們不僅希望視頻顯示尺寸的越來越大,而且視頻顯示質量也要求能達到多畫面、真色彩、高畫質、高分辨率。

在大屏幕拼接系統中,拼接控制器的優劣直接決定著整個大屏幕顯示系統效果的好與壞,目前,拼接控制器的實現方法共三種:第一代PCI插卡式的工作原理是通過工控機,利用多路PCI計算機主板,一部分PCI插槽插入視頻采集卡,另外一部分PCI插槽插入視頻輸出卡,輸入和輸出中間由CPU來構建一個運算和處理中心,這時就組建成了一臺工控式控制器。他的圖形處理原理是通過CPU運算后將母信號分割成M*N個子視頻信號后,再把每一個子信號都進行放大處理分別傳送給拼接幕墻上的各個對應單元,顯示單元將處理器傳送來的信號實現在大屏幕的每個顯示單元上,而分辨率和處理速度由計算機CPU及對應的PCI卡決定,故性能有限。第二代嵌入式拼接器也稱“內拼式拼接器”他是基于液晶屏信號驅動板上增加的運算分割技術,其工作原理先將一個完整的母畫面傳送至信號運算處理器,運算處理器以ID地址編碼器的方式開始鎖定各自在母畫面中的位置,以二進制BCD碼順序排列開始運算切割成多個子畫面,處理器將各自運算好的數據直接輸送給液晶驅動板,驅動板將色彩、亮度、對比度等參數調校后以LVDS方式傳送至LCDIC成像器形成圖像,內拼式拼接器只是單元內部顯示像素的處理,結果是合成顯示圖像,不能解決信號高分辨率拼接和任意位置任意大小多窗口信號處理。第三代拼接系統中控制器采用純硬件處理器FPGA陣列式處理構架,全硬件設計,無CPU和操作系統。控制器集超寬帶視頻信號采集、實時高分辨率數字圖像處理、二維高階數字濾波等高端圖像處理技術于一身,具有強大的處理能力。控制器采用多總線并行處理機制,能從根本上保證對所有輸入視頻進行全實時處理,圖像沒有延遲,無丟楨現象,由于從結構上就超出了前兩代的機器的設計理念,采用純硬件的處理器運算技術,所以啟動時間快,工作非常穩定。

數字化系統產品中,直接采用超大規模、超高速的現場可編程門陣列(FPGA,Field Programmable Gate Array),基于其高集成度、高速、可編程等優點,來實現硬件單片集成,已成為必然趨勢。FPGA豐富的內部資源及高速為實時視頻處理提供解決途徑。

因此,本項目設計基于FPGA的數字視頻處理算法, 實現對DVI視頻信號進行解碼,實時對數字視頻的分割、 視頻圖像的插值放大,并同時將處理結果經DVI編碼送到LCD顯示,完成大屏幕拼接系統的設計。

一、1、系統概述

1.1系統結構

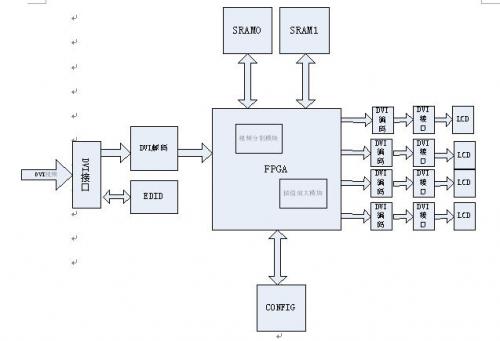

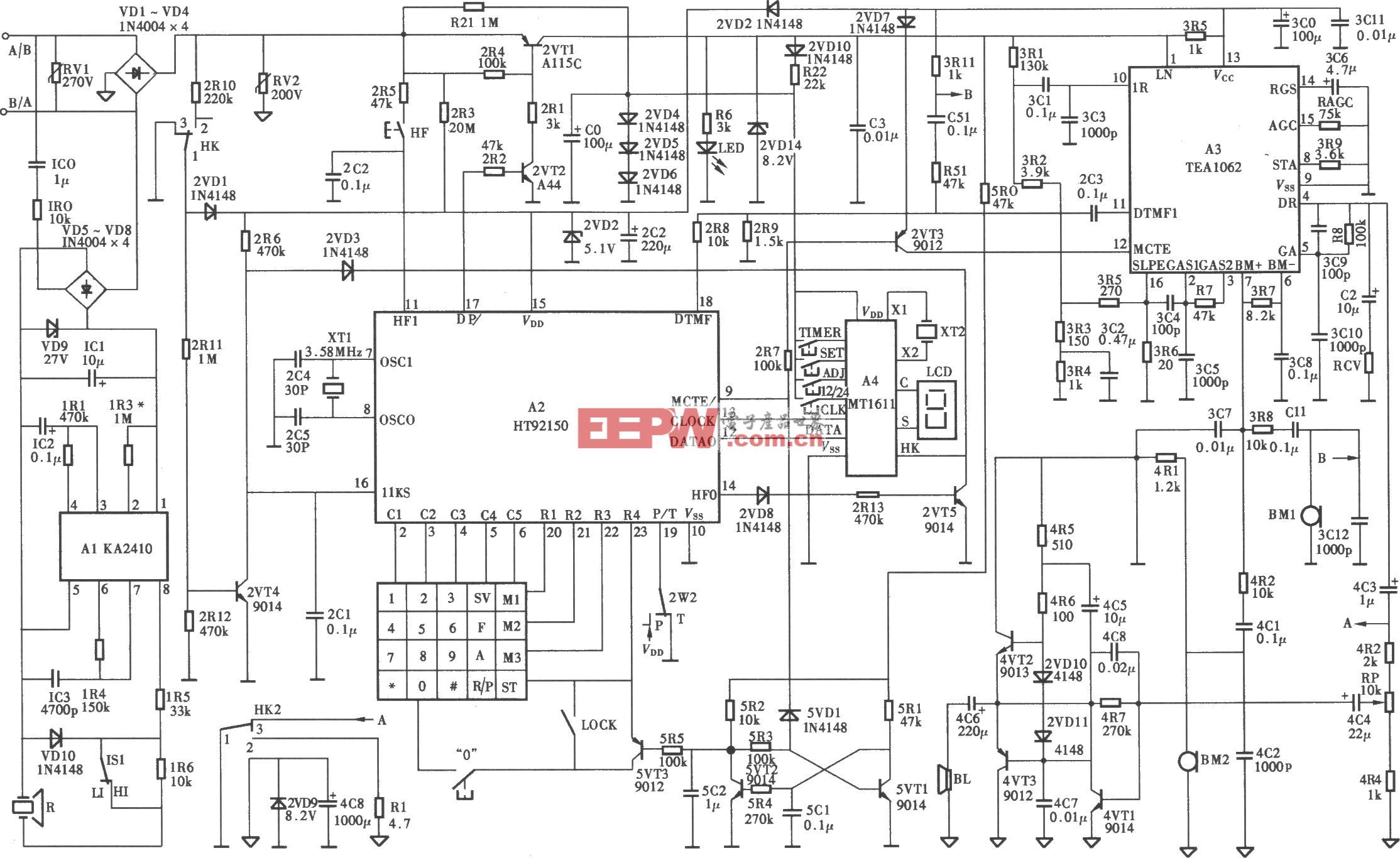

整個LCD屏幕顯示拼接系統包含DVI解碼模塊、視頻分割模塊、SRAM、視頻延展式線性插值放大模塊、視頻輸出控制模塊、DVI編碼模塊等。FPGA 內部邏輯實現將輸入數字視頻分成四路并行的子視頻像素流,經各自獨立的視頻處理通道進行實時插值放大處理。經過視頻編碼電路輸出到由 4個LCD顯示屏組成的拼接屏幕上進行視頻顯示。 應用系統硬件平臺的系統結構設計方案, 如圖1所示。

圖1 LCD屏幕拼接系統結構圖

1.2系統原理

LCD屏幕拼接顯示系統的工作原理, 系統接收一路DVI數字視頻信號, 進行處理前需要先對最小變換差分信號(T.M.D.S.)形式的視頻信號進行解碼(decode)處理, 得到 FPGA 可以處理的像素流信息,經過視頻分割,分割后的子視頻與產生的參考視頻流復合,使各個子視頻的行場同步控制信號一致,各個子視頻經過延展式線性插值放大處理, 得到最小變換差分信號的數字視頻信號, 經 DVI接口輸出到拼接 LCD 顯示器進行顯示。

2、算法實現的功能

算法的主要功能如下: FPGA數字視頻處理電路是對視頻數據進行數字處理的邏輯, 實現實時視頻的預處理、 圖像的分割、 視頻圖像插值放大等處理, 并通過視頻輸出模塊控制四路并行的子視頻同步地顯示到 4個 LCD 拼接屏幕上。 具有以下主要功能:

(1)通過內部邏輯的視頻輸入模塊(VGA Input)接收從DVI解碼電路送出的視頻圖像數據, 包括像素數據(R、 G、 B分量)和視頻同步控制信號(HSYNC、 VSYNC)等, 轉換成預處理的視頻像素流格式。

(2)視頻分割模塊實現原始單幀視頻圖像的分割剪裁, 得到四路完整格式的子視頻像素流 (包含視頻像素數據和視頻同步控制數據), 并控制4個子視頻顯示的相互時序關系; 各個拼接屏幕的像素點的掃描規律相同, 均為逐行掃描形式, 并且子視頻像素點顯示同步, 即行同步和場同步。

(3)視頻插值模塊實現對視頻分割所得的子視頻進行2×2倍地插值放大處理, 該模塊采用并行處理方式, 四路子視頻分別經過各自獨立的視頻處理通道;插值放大算法是基于在FPGA進行延展式線性(extended linear interpolation)待插值像素點的數據計算, 配合視頻生成模塊(VGASyncGen)產生的參考視頻流, 并通過共享的行緩沖存儲器實現插值像素數據的分時讀寫切換來實現的。所得到視頻像素流包含完整視頻像素流格式,并且符合較高分辨率的視頻顯示要求。

(4)視頻輸出模塊,完成放大處理后的各個視頻像素流輸出到DVI 編碼輸出電路。保證各個顯示屏幕得到的視頻信號符合VESA 規定的標準時序要求。

LCD顯示屏相關文章:lcd顯示屏原理

lcd相關文章:lcd原理

評論