基于fpga二維小波變換核的實時可重構電路

1.硬件部分

本文引用地址:http://www.104case.com/article/266432.htm可進化IP核的實現

3.1 實現中的問題

可復用的IP核通常有軟核、固核和硬核三種。本文討論的是軟核。本文的目標是,設計和實現以HDL源代碼(例如,VHDL)表示的可進化IP核。其優點是IP核的表示獨立于平臺,這樣它們就可以在各種不同的目標結構中運行。要解決的主要問題是,可進化的IP核的內部可重構電路的自動重構(因為它們是可進化的)。

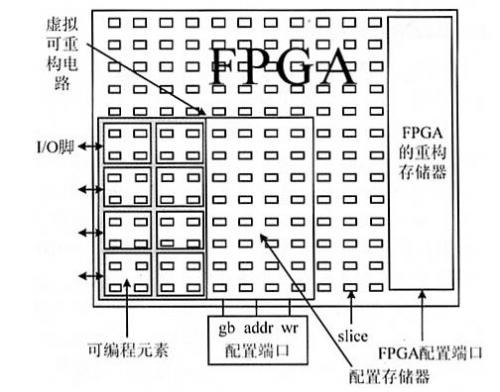

圖 5 用vertex slice 實現的虛擬可重構電路

當一個可進化IP核從一個組件庫中被下載到可重構器件的一個指定位置時,它的內部可重構電路必須進行重構。這就意味著這個可重構器件中的一些可編程塊必須能配置這個可重構器件的其它內部可編程塊。另外,這個可進化IP核(它的基因單元)能被放置于這個可編程陣列(即可重構器件)的任何位置,也就是說,這個可重構器件中必須支持內部重構。

FPGA以其動態可重構的優點,無疑是可進化IP核的最佳實現平臺。然而,通常的FPGA并不支持內部重構,而只允許通過一個特殊的配置接口外部重構(如圖5)。目前,只存在一種支持內部重構的平臺,就是單元陣列,但這種芯片目前還相當少。因此,為了在普通FPGA器件實現可進化IP核,使之能在實際應用中發揮作用,必須采用其它的一些方法。硬件虛擬化是基于FPGA的系統常用的一種設計技術。從這個思想出發,本文采用了一個被稱為虛擬可重構電路的技術來實現可進化硬件中的內部可重構電路。但文中對設計虛擬可重構電路的概念進行了擴展。

3.2 虛擬可重構電路

一些FPGA芯片支持部分重構,也就是允許可重構系統的一部分重構,而不影響其余部分的運行。部分重構的優點在于,其重構所花的時間比全部重構更少。本文以支持部分重構的Xilinx Virtex FPGA為例,來說明虛擬可重構電路的實現。IP核可以動態地下載到FPGA或從FPGA刪除。所有的操作都通過Virtex重構端口和Jbits接口來完成。當一個可進化IP核被下載時,它的重構位串在指定位置構靠下列單元;虛擬可重構電路、基因單元和控制器。

圖5表明,虛擬可重構電路實際上是一種在普通FPGA上實現的新的可重構電路。本例中由八個可編程元素構成,由Virtex單元(slice)實現。Virtex單元實現新的可編程元素陣列、新的布線電路和新的配置存儲器。虛擬電路能內部重構,但如果有其它新的配置存儲器與之連接,也可從FPGA的I/O引腳配置。

這種方法的優點在于:可根據具體的應用需要準確地設計可編程元素陣列、布線電路和配置存儲器。虛擬可重構電路的重構方式和粒度能準確地反映具體應用的需要。通過虛擬可重構電路,很容易把領域知識插入到基因單元和可重構電路的體系結構中,從而獲得電路軟件模型的精確實現。

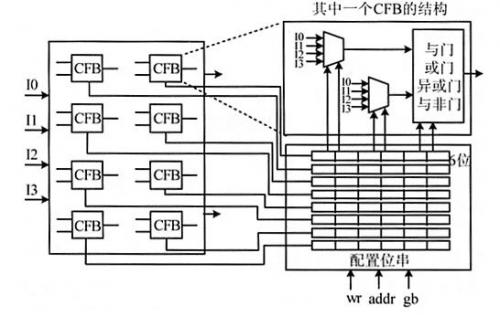

圖6給出了一個虛擬可編程元素的例子。這個虛擬可重構電路由8個這樣的元素構成,有4個輸入和2個輸出。這些虛擬可編程元素稱為可重配置功能塊CFB(Configurable Functional Blocks)。每個CFB對應一個配置位串(這里的位串為6位),其中兩個配置位決定了CFB的功能,其它四位定義了輸入的連接信息。布線電路由多路器組成,它們由配置存儲器中的位串控制。配置存儲器由Virtex單元構成,一個Virtex單元包含兩個觸發器,用于存儲配置位串中的兩位。配置存儲器的所有位都連到多路器,多路器控制布線和CFB中功能的選擇。

虛擬可重構電路中CFB的數量由具體的應用決定。虛擬可重構電路用結構級VHDL語言來描述,但是一些基本的電路(例如“MAX”電路)用行為級來描述。虛擬可重構能在不同的目標器件下綜合,目標器件并不需要支持部分重構。

圖 6 虛擬可重構電路及其中一個CFB的實現

3.3 基因單元和控制器

基因單元和控制器的實現通常有兩種選擇:采用普通微處理器實現,或者設計一個專用的電路來實現。

專用的電路是指一種進化算法的硬件實現,目前在可進化硬件領域已經開發了很多這樣的實現。這種算法的優點是電路的進化速度快,適合于復雜的應用。

采用微處理器實現時,可以購買或免費獲得現成的微處理器軟核,如Xilinx提供的MicroBlaze和PicoBlaze微控制器IP核,Altera生產Nios核,等等。此外,如果給出的目標可重構器件中有片上處理器,可以使用片上處理器,Xilinx Virtex II Pro XC2VP50芯片包含四個PowerPC處理器。處理器必須通過編程來執行程序,它們能和核周圍的環境進行通信并完成對染色體的基因操作。此外,處理器還負責內部虛擬可重構電路的重構。

評論