基于USB3.0和FPGA的多串口傳輸系統設計

3.1邏輯模塊設計

本文引用地址:http://www.104case.com/article/265047.htm系統的邏輯模塊分為時鐘模塊、FX3發送/接收緩存模塊、發送/接收控制模塊、FX3讀寫控制模塊、485接收模塊、485發送模塊以及配置串口參數模塊。

整個系統的數據流分為兩個過程:485數據采集過程和485發送控制命令過程。

(1)485數據采集過程:485數據通過485接收模塊傳送給FX3接收緩存模塊,在FX3數據接口沒有被占用時,通過FX3讀寫控制模塊發送給USB3.0芯片并傳到PC端。

(2)485數據發送過程:USB3.0芯片通過FX3讀寫控制模塊將數據發送到FX3發送緩存模塊中,在收發控制模塊檢測到相關串口空閑后通過485發送模塊將相關數據發送出去。

485收發相對于USB3.0速度來說,屬于慢速設備。為了提高USB3.0總線利用率,此處只設計了兩種緩存,即接收緩存和發送緩存,大小都設置為512KB,80路的485接收和發送buffer最終都匯聚到這兩種緩存上,有效地減少了短包和空包發生率。

3.2 FX3接口時序

FPGA與FX3之間采用了Slavefifo模式,FPGA通過狀態標志的flaga、flagb、flagc、flagd來判斷FX3的接收/發送緩存的數據狀態,當flaga/flagc為高時,表示FX3緩存中接收到了數據;當flagb/flagd為高時,表示FX3的發送緩存為非滿狀態,FPGA可對其進行寫數據操作。

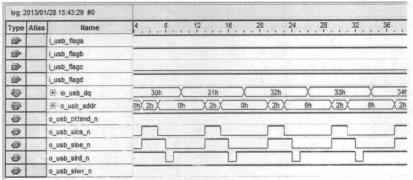

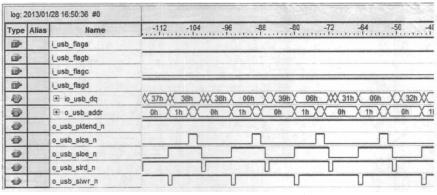

圖3所示為FX3的A通道讀時序,FPGA先檢測i_usb_flaga是否為高電平,如果為高電平則表示A通道buffer中有數據可讀,此時將通道地址信號設置為0,片選信號o_usb_slcs_n/o_usb_sloe_n拉低,o_usb_slrd_n信號拉低后,在4個時鐘之后,數據將出現在io_usb_dq上,如果進行寫操作則將o_usb_slwr_n拉低。對應的通道號地址選對,同時將片選信號拉低即可,寫通道時序如圖4所示。

圖3 FX3的A通道數據讀取時序

圖4 FX3的B通道寫數據時序

4通信速度實驗結果

利用Cypress的Streamer軟件,可以測試該USB3.0傳輸系統的傳輸速率。將Packets per Xfer設置為256,在win764位下(電腦配置為華碩N53XI241SN,Fresco FL1000系列的控制器)的傳輸速率測試結果為2.5Gb/s,滿足了整個系統的性能,如圖5所示。

圖5讀速率測試結果圖

該系統適合于超高速數據的傳輸,具有電路簡單、體積小等優點。FPGA技術與USB3.0的結合有極大的靈活性和可擴展性,基于FPGA和USB3.0的突出優點,該設計方案必將應用在更廣闊的領域。

數字通信相關文章:數字通信原理

通信相關文章:通信原理

評論