為何Zynq SoC平臺可以使企業(yè)的產(chǎn)品利潤激增(二)

平臺:實(shí)現(xiàn)盈利衍生品的最佳戰(zhàn)略

本文引用地址:http://www.104case.com/article/263142.htm面對不斷增加的研發(fā)成本、日漸激烈的競爭以及消費(fèi)者對更好產(chǎn)品日益苛刻的需求,越來越多的半導(dǎo)體公司和電子產(chǎn)品系統(tǒng)公司開始轉(zhuǎn)向?qū)で笃脚_戰(zhàn)略來快速創(chuàng)建衍生產(chǎn)品并最大限度提高盈利性。平臺戰(zhàn)略能夠進(jìn)一步降低產(chǎn)品開發(fā)時(shí)間、加速上市進(jìn)程并節(jié)省工程時(shí)間成本,同時(shí)能夠提高各種衍生產(chǎn)品或新一代產(chǎn)品的盈利性。

正如IBS研究所顯示,企業(yè)通過開發(fā)衍生設(shè)計(jì)“優(yōu)化收入和利潤”。而采用平臺方法在相同節(jié)點(diǎn)開發(fā)多種衍生產(chǎn)品(也就是說,衍生產(chǎn)品的衍生產(chǎn)品)使企業(yè)能夠進(jìn)一步優(yōu)化收入與利潤,因?yàn)楦鱾€(gè)后續(xù)設(shè)計(jì)都能受益于在之前設(shè)計(jì)中學(xué)到的經(jīng)驗(yàn)教訓(xùn)、重新利用以及對客戶需求更準(zhǔn)確的了解。

處理選擇是平臺成功的關(guān)鍵

企業(yè)在實(shí)施平臺戰(zhàn)略時(shí)做出的兩項(xiàng)最重要的業(yè)務(wù)決策實(shí)際上是關(guān)鍵技術(shù)決策:眾多處理系統(tǒng)中哪一個(gè)會(huì)成為產(chǎn)品平臺的核心?該處理系統(tǒng)的哪種芯片實(shí)施方案最適合提高盈利性?

在平臺戰(zhàn)略中,處理系統(tǒng)必須滿足或者超過應(yīng)用軟件和系統(tǒng)需求。它必須具備可擴(kuò)展性并且易于擴(kuò)展;必須具有不斷增長的大型成熟生態(tài)系統(tǒng);而且必須允許設(shè)計(jì)人員和工程師利用之前的設(shè)計(jì)成果。最后,它必須來自具有發(fā)展規(guī)劃且成熟穩(wěn)定的供應(yīng)商,而且該供應(yīng)商并未持有偏離其發(fā)展規(guī)劃或者不斷推出無盡勘誤的不良記錄。雖然有一些候選產(chǎn)品符合上述某些要求,但是能夠滿足或超過全部上述要求的系統(tǒng)是ARM微處理器架構(gòu)。

|

|

生命周期收入* (百萬美元) |

研發(fā)支出(百萬美元) |

生命周期凈利潤** (百萬美元) |

凈現(xiàn)值*** (百萬美元) |

盈利能力指數(shù) |

|

初始復(fù)雜ASIC |

$1300 |

$130 |

$260 |

$12.85 |

0.1 |

|

1號衍生品 (80%市場規(guī)模) |

$1040 |

$35 |

$208 |

$74.78 |

2.14 |

|

2號衍生品(80%市場規(guī)模) |

$650 |

$35 |

$130 |

$34.47 |

0.98 |

* 假設(shè)7年。

** 假設(shè)利潤率為20%。

*** 假設(shè)貼現(xiàn)率為15%。

表1 – 開發(fā)衍生設(shè)計(jì)具有可觀的凈現(xiàn)值(NPV)和更加出色的盈利性指數(shù)。

ARM已經(jīng)成為PC之外一切設(shè)備的事實(shí)標(biāo)準(zhǔn)嵌入式架構(gòu)。如今采用高級嵌入式處理技術(shù)的絕大部分電子系統(tǒng)——從手機(jī)、汽車到醫(yī)療設(shè)備——都采用ARM處理器內(nèi)核。尤其是ARM的Cortex-A9處理器架構(gòu)成為許多種片上系統(tǒng)(SoC)的核心。其不僅已用于專門針對前言智能手機(jī)、平板電腦等高量產(chǎn)增值產(chǎn)品開發(fā)的ASIC設(shè)計(jì)中,而且還用于眾多ASSP設(shè)計(jì),該設(shè)計(jì)主要針對那些希望進(jìn)軍由于缺乏功能差異化而主要展開價(jià)格競爭的中小規(guī)模成熟市場的公司而開發(fā)。

為了增強(qiáng)產(chǎn)品差異化,許多企業(yè)基于ARM處理系統(tǒng)創(chuàng)建了將FPGA與現(xiàn)成ASSP融為一體的產(chǎn)品平臺。他們可以在這種配置中實(shí)現(xiàn)硬件與軟件細(xì)分,從而創(chuàng)造更廣泛的特性組合或者靈活、可升級、性能更高的終端產(chǎn)品——其可幫助他們戰(zhàn)勝那些提供仿效式僅可軟件編程的ASSP實(shí)施方案的競爭對手。在這些ASSP中添加賽靈思FPGA已經(jīng)幫助眾多企業(yè)的產(chǎn)品在市場中脫穎而出。

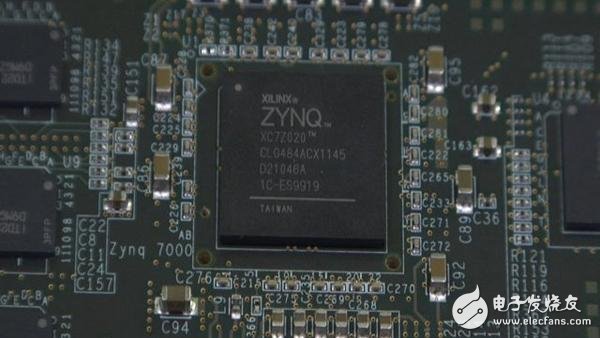

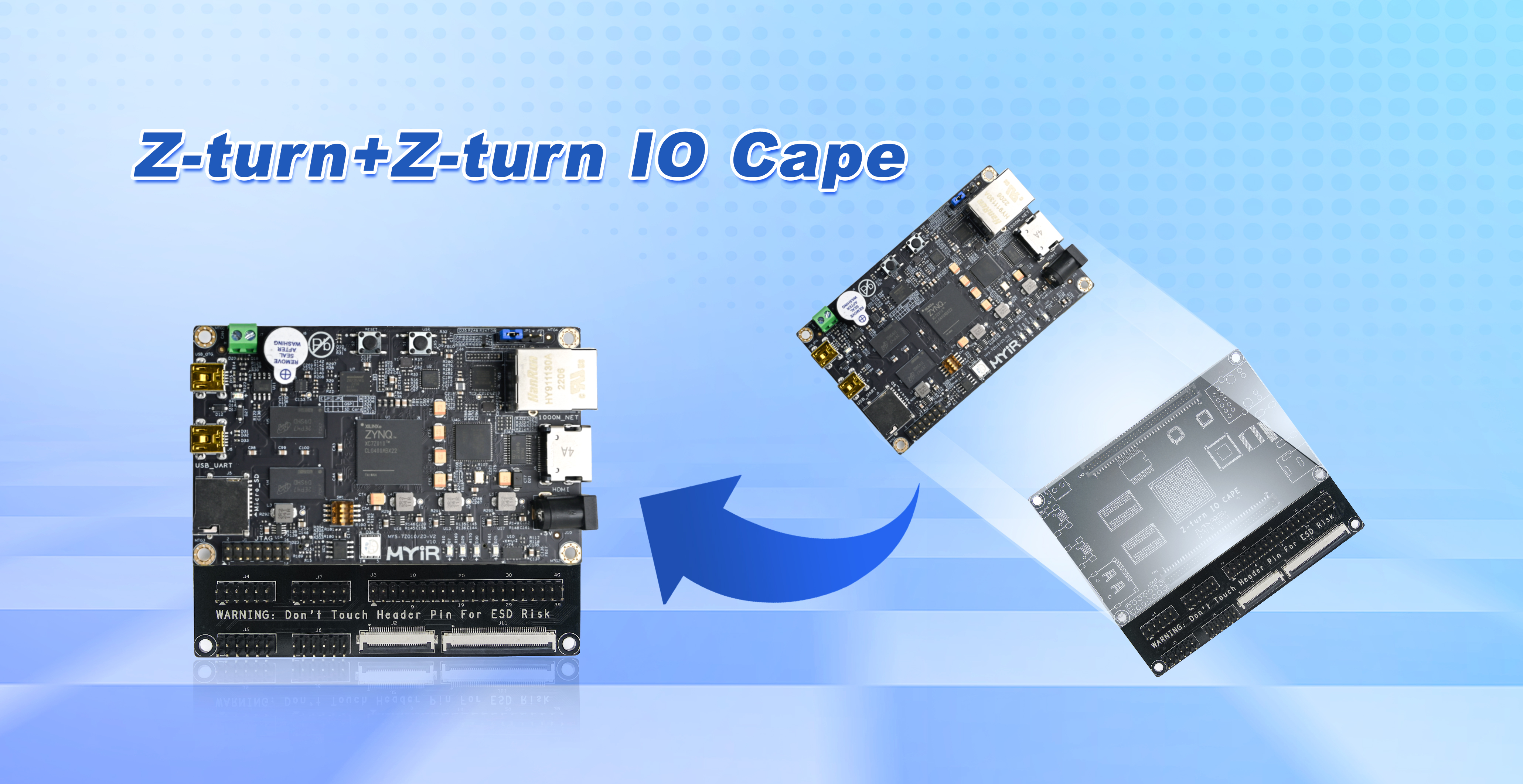

理想平臺解決方案:ZYNQ SoC

借助Zynq-7000 All Programmable SoC,賽靈思正在實(shí)施適合絕大部分嵌入式應(yīng)用的高穩(wěn)健性ARM Cortex- A9平臺解決方案。如表2所示,作為一種芯片平臺,Zynq SoC具備超過ASIC、ASSP以及ASSP+FPGA組合的眾多優(yōu)勢。與ARM處理系統(tǒng)的其他硬件實(shí)施方案相比,Zynq SoC不僅在NRE、靈活性、差異化、生產(chǎn)力/上市進(jìn)程等方面具有最佳特性組合,而且還具有最低衍生品成本和最低整體風(fēng)險(xiǎn)(表3)。

另外,Zynq-SoC與其他平臺實(shí)施方案相比具有巨大的成本優(yōu)勢。讓我們來看一下具體數(shù)據(jù)。

賽靈思 All Programmable SoC產(chǎn)品營銷與管理總監(jiān)Barrie Mullins表示,設(shè)計(jì)28nmASIC的平均成本是1.3億美元,而ASIC設(shè)計(jì)項(xiàng)目的10倍收入目標(biāo)則為13億美元。他指出,但是,基于Zynq SoC的典型設(shè)計(jì)項(xiàng)目本質(zhì)上其整體設(shè)計(jì)成本比ASIC實(shí)施方案低得多而且上市進(jìn)程也比其快。其原因是Zynq SoC能夠提供預(yù)設(shè)計(jì)、特征化、業(yè)經(jīng)測試與驗(yàn)證的成品SoC,其可以帶來軟件、硬件、I/O性能以及差異化靈活性。此外,Zynq SoC還受益于低成本且高度集成的賽靈思硬件與軟件設(shè)計(jì)工具,而ASIC工具流程不但復(fù)雜,而且具有嚴(yán)重的互操作性及兼容性問題,同時(shí)還需要支付高達(dá)數(shù)百萬的許可費(fèi)用。設(shè)計(jì)人員采用賽靈思推薦的UltraFast™方法時(shí)賽靈思的設(shè)計(jì)流程會(huì)尤為優(yōu)化。Mullins補(bǔ)充到,由于賽靈思生態(tài)系統(tǒng)IP已經(jīng)完成設(shè)計(jì)和預(yù)驗(yàn)證并且賽靈思工具可以生成中間件,因此IP認(rèn)證成本較低。

|

|

系統(tǒng)總成本 |

靈活性 |

差異化 |

上市進(jìn)程 |

衍生品成本 |

風(fēng)險(xiǎn) |

|

Zynq SoC |

低+最高價(jià)值 |

最靈活:硬件與軟件可編程性 + 可編程I/O |

可編程性最高,硬件/軟件協(xié)同設(shè)計(jì) |

集成硬件與軟件差異化速度最快 |

硬件與軟件可編程性帶來最低成本 |

可預(yù)測的低風(fēng)險(xiǎn) |

|

ASSP + FPGA |

高于Zynq SoC (與系統(tǒng)相關(guān)) |

非常靈活,但是與Zynq SoC相比ASSP I/O有局限性 |

硬件與軟件可編程性取決于ASSP |

如果ASSP需要硬件細(xì)分,則速度最快 |

中低成本,取決于FPGA廠商 |

中低風(fēng)險(xiǎn),取決于FPGA廠商 |

|

ASSP |

如果只需純軟件可編程性,則最低 |

良好靈活性,但是僅具備軟件可編程性 |

僅具備軟件可編程性 – 便于克隆 |

如果僅需純軟件細(xì)分,則速度最快 |

如果需要純軟件衍生品,則成本最低 |

如果僅需純軟件可編程性,則有可能風(fēng)險(xiǎn)最低 |

|

ASIC |

極高,以致無法承擔(dān)。 |

制成后僅具備有限軟件靈活性 |

最佳硬件細(xì)分,但是軟件細(xì)分有局限性 |

速度最低且風(fēng)險(xiǎn)最高 |

最高 |

極高(重新設(shè)計(jì)) |

最佳平臺特性

良好平臺特性

一般平臺特性

最差平臺特性

表2 – Zynq-7000 All Programmable SoC可為尋求實(shí)施平臺戰(zhàn)略的客戶提供理想的特性組合。

|

最低NRE與最佳風(fēng)險(xiǎn)降低 |

最高靈活性與差異化 |

更高生產(chǎn)力與更快上市進(jìn)程 |

最低衍生品成本與最高盈利性 |

|

√ 成品芯片 √ 開發(fā)與設(shè)計(jì)工具成本微不足道 √ 賽靈思IP庫 + 第三方IP √ 廣泛的開發(fā)板 |

√ All Programmable 硬件、軟件與I/O √ 具備隨時(shí)現(xiàn)場可編程性 √ 部分重新配置 √ 安全的系統(tǒng)(加密) |

√ 即時(shí)硬件/軟件協(xié)同開發(fā) √ All Programmable 抽象(C、C++、OpenCV、OpenCL、HDL、基于模型的輸入) √ Vivado Design Suite、Vivado HLS、IP Integrator 與 UltraFast方法 √ 廣泛、開放的OS與IDE支持(開源Linux及Android、FreeRTOS、Windows Embedded、Wind River、Green Hills等) |

√ 基于ARM AMBA AXI4實(shí)現(xiàn)IP標(biāo)準(zhǔn)化 √ 重新利用預(yù)驗(yàn)證代碼(ISO、FCC等) √ 重新利用和優(yōu)化代碼與測試文件 √ 量產(chǎn)芯片、電源電路、PCB與IP許可授權(quán)。 |

表3 – 低NRE費(fèi)用、靈活性等要素使Zynq SoC成為平臺戰(zhàn)略的理想選擇。

Mullins指出,因此典型Zynq SoC項(xiàng)目需要2300萬美元。由此實(shí)現(xiàn)設(shè)計(jì)項(xiàng)目的標(biāo)準(zhǔn)10倍收入目標(biāo)需要生命周期收入達(dá)到2.3億美元——此10倍目標(biāo)比實(shí)現(xiàn)ASIC實(shí)施方案所需達(dá)到的13億美元10倍目標(biāo)更易于實(shí)現(xiàn),而且也更可行(表4)。

采用的上述方法分析IBS數(shù)據(jù)時(shí),如果我們假設(shè)在Zynq SoC 中實(shí)現(xiàn)的初始復(fù)雜設(shè)計(jì)能夠完全占領(lǐng)同樣的13億美元目標(biāo)市場,則利用57名工程師只需要2300萬美元就能夠在兩年內(nèi)完成產(chǎn)品。

如果假設(shè)初始Zynq SoC設(shè)計(jì)具有與初始ASIC設(shè)計(jì)相同的20%利潤率,則初始Zynq SoC設(shè)計(jì)的NPV為1.0727億美元,而PI為3.7,其明顯優(yōu)于初始ASIC的1285萬美元NPV和僅有0.1的PI。利潤率同樣為20%的Zynq SoC的NPV與PI更加可觀(表5)。

|

|

28nmASIC(IBS數(shù)據(jù)) |

|

Zyng SoC (賽靈思估算) |

|||

|

% |

大概工程月數(shù) |

總成本(百萬美元) |

% |

大概工程月數(shù) |

總成本(百萬美元) |

|

|

硬件 |

|

|

|

|

|

|

|

IP認(rèn)證 |

26 |

704 |

11.8 |

20 |

240 |

4.0 |

|

架構(gòu) |

8 |

209 |

4.2 |

45 |

100 |

2.1 |

|

驗(yàn)證 |

53 |

1431 |

28.9 |

35 |

160 |

3.0 |

|

物理設(shè)計(jì) |

13 |

350 |

6.9 |

0 |

0 |

0 |

|

硬件小計(jì)(設(shè)計(jì)工程資源) |

100 |

2694 |

51.8 |

100 |

500 |

9.1 |

|

軟件 |

|

4296 |

59.8 |

|

720 |

10.0 |

|

原型成本(百萬美元) |

2.1 |

1.0 |

||||

|

原型驗(yàn)證 |

|

815 |

16.6 |

|

140 |

2.8 |

|

總計(jì) |

|

7805 |

130.3 |

|

1360 |

22.9 |

c++相關(guān)文章:c++教程

評論