3.7 GHz寬帶CMOS LC VCO的設計

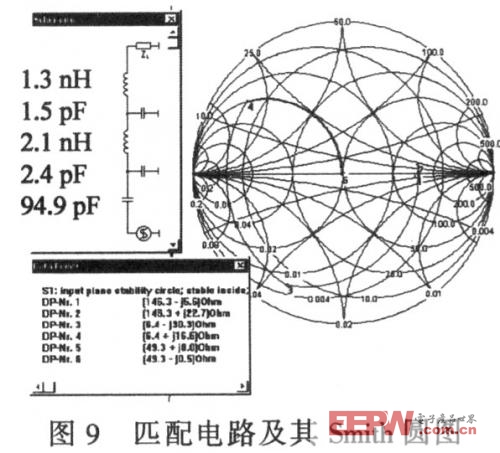

當開關處于OFF狀態時,開關電容

振蕩頻率正比于![]() 因此調節范圍取決于最大電容和最小電容的比值,由式(3)、(4)可以得到最大電容和最小電容的比值為

因此調節范圍取決于最大電容和最小電容的比值,由式(3)、(4)可以得到最大電容和最小電容的比值為

![]()

從公式(5)、(6)可以看到開關電容最大的Q值與最大的調節比率之間存在沖突。C0由工作頻率w0決定,因此Wsw在優化中是最重要的設計參數。

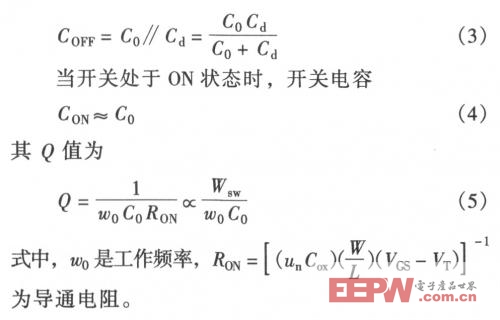

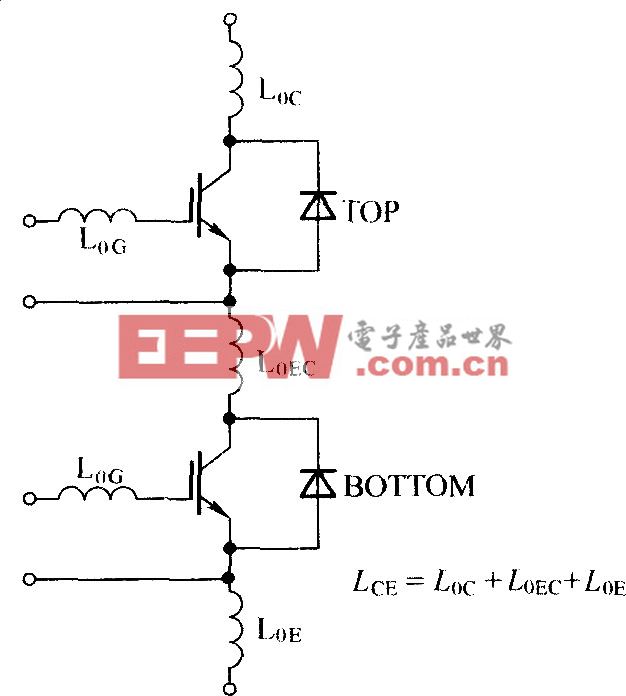

開關電容的Q值可以通過差分電容開關的方式來改善,如圖7所示。當開關處于ON狀態的時候只有溝道電阻RON的一半與電容串聯,相比于單端的結構,Q值可以提高一倍。M2和M3為工作在亞閾值區的有源電阻,可以為MOS開關的源端和漏端提供直流偏置。

當Vsw設為0的時候,VD/S=0,VG=VDD,因此MOS開關管的VGs—VT達到最大,從差分端口看進來,等效電容達到最大,因此電路振蕩在較低的頻率上;當Vsw設為VDD時,VD/S=VDD,VG=0 V,電路工作在較高的頻率上。

1.4 輸出緩沖器及匹配電路的設計

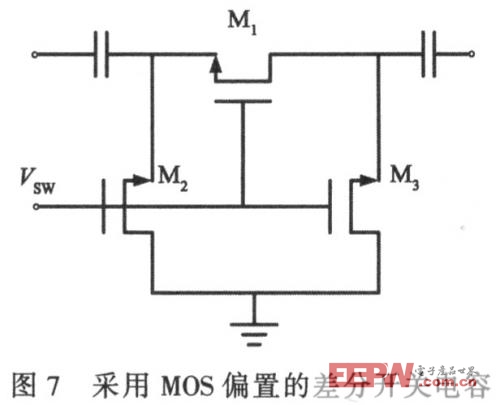

為了將VCO的輸出信號送到片外,考慮到外部電容很大,采用了電感負載的緩沖器,通過選擇合適的電感和電容使其諧振在3.7 GHz,如圖8所示。

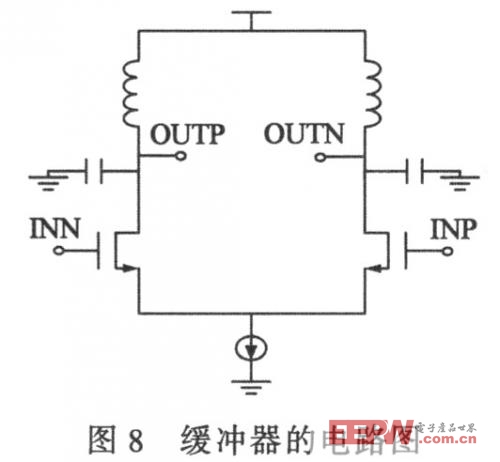

在匹配電路的設計上,選用了π型匹配電路,首先利用spectreRF仿真得到輸出緩沖器的S22參數,然后構建匹配電路使其阻抗達到50 Ω。具體的匹配電路(1.3 nH為邦線電感,94.9 pF的電容為隔直電容)及其Smith圓圖如圖9所示。

2 測試結果

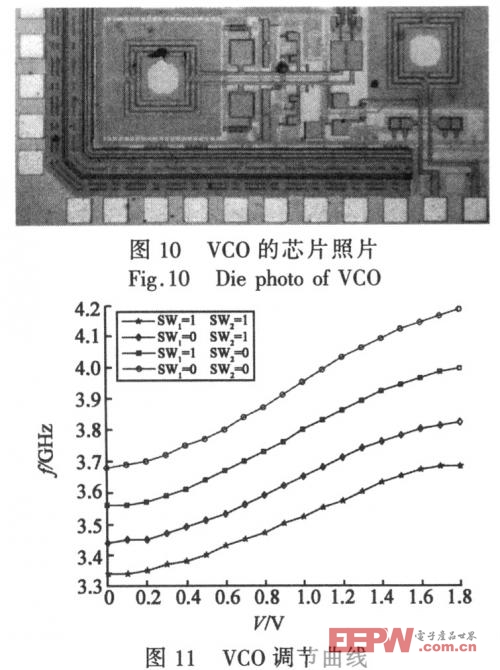

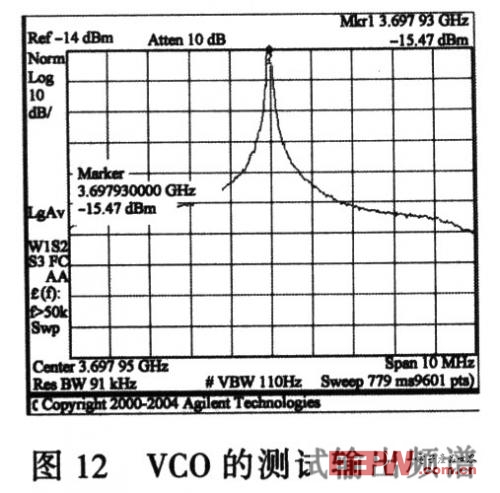

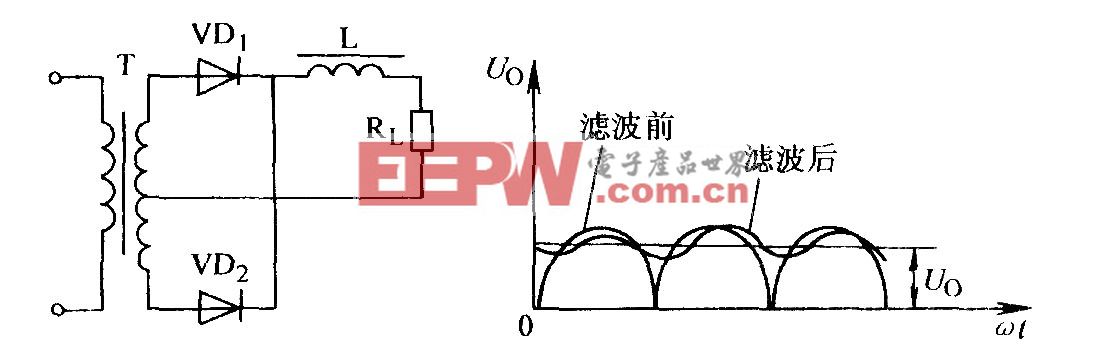

本LCVCO是用于3.7 GHz鎖相環的,整個鎖相環是在和艦0.18μm混合信號工藝下制造的,整個VCO的面積為0.4 mm×1 mm,芯片照片如圖10所示。測試得到的VCO的工作頻率為3.4~4 GHz,有16%的調節范圍,調節電容陣列開關得到的頻率隨控制電壓的變化曲線如圖11所示。在1.8 V電源電壓下的功耗為10 mW;在1 MHz頻偏處的相位噪聲為一100 dBc/Hz。測試得到的VCO輸出頻譜如圖12所示,輸出功率相對較低,主要是由于對邦線的寄生電感和寄生電容估計出現偏差導致匹配電路沒有實現完全匹 配,但這對VCO性能的測試沒有實質的影響。

3 結論

基于和艦0.18μmCMOS混合信號工藝設計了一款工作在3.7 GHz的LCVCO。本文著重論述了電感與射頻開關的設計,通過采用電容開關陣列的方式增加了VCO的工作范圍以補償PVT的變化所帶來的影響。測試結果表明,該VCO可用于鎖相環和頻率合成器。

評論