數字射頻存儲器用GaAs超高速3bit相位體制ADC的設計與實現

3、工藝實現

電路采用南京電子器件研究所標準GaAsΦ76mm 全離子注入工藝實現,器件均為耗盡型器件,為非自對準常規工藝。工藝流程簡介如下:N- 有源區采用大面積Si 離子注入形成,注入能量為60keV,劑量為4.3 ×1012 cm-2;N+ 區采用Si 離子選擇雙注入形成,注入能量分別為120,60keV,劑量均為3 ×1013cm-2;源漏歐姆接觸金屬采用Au/ Ge/ Ni 金屬系統,柵采用常規Ti/ Pt/ Au 柵。整個流程應用金屬剝離工藝,電路用Si3N4 介質實現兩層金屬布線隔離。嚴格控制柵挖槽工藝,調整器件的閾值電壓到目標電壓-1.3V。最終得到的芯片實際照片如圖5 所示,芯片尺寸為2mm ×2mm,各功能模塊均以框圖標示。

4、電路測試

設計測試專用的測試盒及高速PCB 板,芯片直接裝配到測試底座上,通過金絲鍵合至PCB 上的傳輸線。由于電路本身含有驅動50Ω 負載的輸出緩沖驅動電路,因此,測試過程中電路存在比較大的高速開關電流。為了保證在這種電流急速開關變化下的信號完整性,需要對所有的直流饋線交流旁 路,旁路電容采用1μf 和100pf 的貼片電容,以此來穩定直流饋電的電壓穩定。由于電路的量化對象是相位量,所以需要嚴格避免輸入輸出電纜給各通道所引入的額外相位誤差。以每個通道輸出信 號經過各自高低電平的50 %點為基準進行相位差統計。圖6 為高頻150MHz 輸入模擬正交信號、2GHz 時鐘速率下的測試結果,ADC 的輸出碼流速率均為1.2Gbp s。由圖可見,電路各通道的相位關系正確,輸出幅度在50Ω 負載上均有180mVpp 的擺幅。

圖5、3bit 相位體制ADC 芯片照片

圖6、150MHz 輸入、2GHz 時鐘速率下的輸出波形

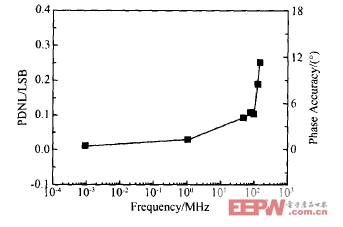

相位量化ADC 最關鍵的參數是相位精度隨工作頻率的變化情況,它決定了ADC 電路的瞬時工作帶寬。在某一頻率f 下,Pha(i)代表實際第i 個碼元所對應的相位量,那么該頻率下的相位精度PA(f)可表示為:

PA(f)= max(abs(Pha(i)- 45)) i = 1,2 ?,8

同傳統的幅度ADC,也可以用線性度隨工作頻率的變化描述電路的頻域性能。定義PDNL(f)代表該頻率下的微分線性度,則:

PDNL(f)= PA(f)/ 45

圖7 是該電路的微分非線性誤差及相位精度隨頻率的變化特性。

圖7、PDNL 及相位精度的動態性能

功分器相關文章:功分器原理

評論