AESA雷達信號處理及體系結構

主動電掃描陣列(AESA)雷達是當今先進武器系統的關鍵組成,特別是機載作戰系統。而其體系結構的未來發展將超越最初的軍事應用,延伸到地球物理測繪、汽車輔助駕駛、自動車輛、工業機器人和增強現實等領域:實際上,這包括任何需要對大量的傳感器數據進行調理,融合到模型中進行判決的應用。

隨著AESA體系結構的擴展,它們將突破雷達信號處理專業應用,延伸到其他應用中。在外部應用中,這些設計會遇到典型的嵌入式設計流程:以CPU和軟件為中心的,基于C的以及與硬件無關的。本文中,我們將介紹先進的掃描陣列雷達,從經驗豐富的雷達信號處理專家的角度以及傳統的嵌入式系統設計人員的角度來研究其體系結構。

典型系統的角色

掃描陣列和傳統移動盤式雷達的不同在于天線。掃描陣列并沒有采用熟悉的連續旋轉拋物線天線,而是在大部分系統中采用了平面靜止天線。陣列并不是有一個單元聚焦在反射器上,而是有數百上千個單元,每個單元都有自己的收發器模塊。系統電子電路處理每一單元信號的振幅和相位,形成雷達波束和接收方向圖并聚焦,設置定義總天線方向圖的干涉方向圖。

這一方法避免了采用大量的移動部件,支持雷達實現傳統天線采用物理方法無法獲得的功能,例如,瞬時改變波束方向,發送和接收同時有多個天線方向圖,或者把陣列分成多個天線陣,完成多項功能——也就是,根據地形搜索目標,同時跟蹤目標。這些方法只需要在發送器增加一些信號,在每一接收器將信號分開。重疊是一種很好的方法。

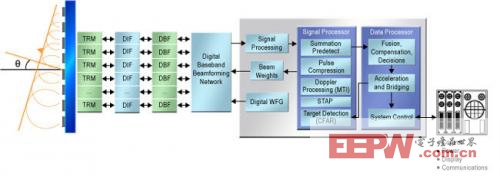

一個完整的系統從CPU簇傳輸到天線,然后再返回(圖1 )。一開始處理時,軟件控制的波形發生器產生系統要發送的啁啾。取決于應用,降噪、多普勒處理和隱身的需求會對信號有所損傷。

圖1 .一個非常簡化的AESA系統結構圖。

波形發生器將信號送到聚束網絡中。在這里,信號被連接至每一發送通道。在這一級,數字復用器在通道上應用振幅權重來實現空間濾波,對波形整形。這一步也可以稍后再做。在很多設計中,每一通道的信號現在會通過一個數模轉換器(DAC),然后輸入到模擬IF和RF上變頻器中。RF上變頻后,信號到達獨立的發送器模塊,附加上相移或者時延,調整振幅(如果在基帶沒有做),最終進行濾波和放大。

一開始,接收到的信號實際上通過與反方向相同的通路,在后端要進行更多的處理。在每一個天線單元,限幅器和帶通濾波器保護了低噪聲放大器。放大器驅動RF下變頻器,可以結合模擬放大和調相功能。信號從IF級傳輸到基帶,每一天線單元的信號到達其模數轉換器(ADC)。然后,聚束模塊把天線信號重新組合成一路或者多路復數數據采樣流,每一數據流代表了來自某一接收波束的信號。這些信號流通過大占空比的數字信號處理(DSP)電路,進一步調理數據,進行多普勒處理,嘗試從噪聲中提取出實際信號。

什么時候進行數據轉換

在很多設計中,大部分信號處理工作是以模擬方式完成的。但是,隨著數字速度的提高,功耗和成本的降低,數據轉換器與天線靠的越來越近。Altera應用專家Colman Cheung建議了一個理想的系統,直接從DAC驅動天線單元。但是,2013年,這類設計在技術上還無法實現,特別是,trans-GHz RF.

目前可以把數據轉換器放在IF中,進行IF頻率轉換,所有基帶處理工作都是數字化的(圖2)。可以在基帶聚束網絡中,以數字方式在天線單元之間產生干涉方向圖的時延,每一個天線單元并不需要模擬相移器或者延時線。這種劃分方法支持DSP設計人員把發送和接收通路分解成分立的功能——乘法器、濾波器、用于延時的FIFO,以及加法器,在MATLAB中對其進行建模,從庫中實現它們。可以把要求最苛刻的功能放到專門開發的ASIC、FPGA或者GPU芯片中,而把要求不太高的運算分組成DSP芯片或者加速器中的代碼。

圖2 .把數據轉換器放到IF級的最后。

需要特別注意信號從聚束網絡出來后的接收鏈信號處理,這是因為其存儲器和處理需求會非常大,涉及到的動態范圍非常寬——從干擾發射器輸入到搜索探測范圍的每一邊沿。會需要高精度浮點硬件,還需要更強的處理能力。

在其最后級,有目的的對接收鏈進行修改并實現。通過其濾波、聚束和脈沖壓縮級,鏈的任務是從噪聲中提取出信號,特別是那些可能承載了環境中實際目標信息的信號。然后,重點從信號轉向它們所代表的目標,任務的本質發生了改變。

從信號到目標

脈沖壓縮是這一抽象過程的開始。在時間域或者頻域,脈沖壓縮器一般通過自相關找到有可能含有發送啁啾的波形。然后,它采用脈沖目標來表示這些波形——含有到達時間、頻率和相位以及其他相關數據的數據包。從這里開始,接收鏈會處理這一數據包而不是接收到的信號。

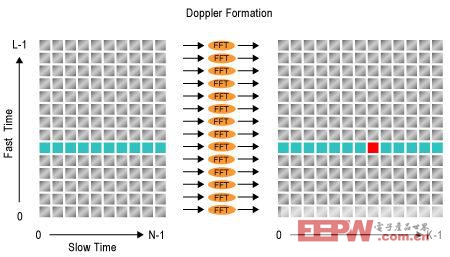

下一步一般是多普勒處理。首先,脈沖被送入方格陣列中(圖3 )。在陣列中,每一列含有從某一發射器啁啾返回的脈沖。陣列中會有很多列,這取決于系統能夠承受多大的延時。陣列中的行表示返回切換時間:距離陣列的x軸越遠,發射器啁啾和接收脈沖到達時間之間的延時就越大。這樣,延時方格也代表了與某一脈沖反射的目標的距離。

圖3 .多普勒處理方格。

評論