C語言在FPGA上實現DSP的解決方案

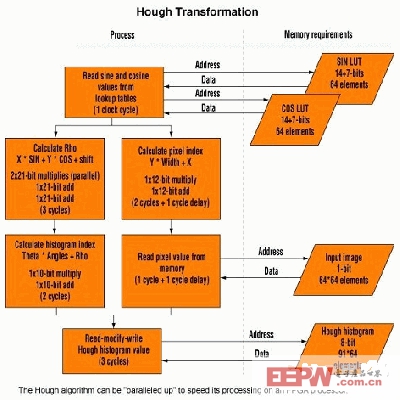

最后,你還必須分析各個算法,將其按步分解成由數學運算(加、減、乘、除、積分)、延遲、保存到內存和查表等操作。無論多復雜的算法都可以分解成這些最基本的操作,而且這些操作在相互無關聯的情況下可以并行處理。我們的示例應用可以這樣被加速:9個處理周期被充分地進行管道處理,在初始延遲后的每個時鐘都輸出一個結果,然后這些周期被嵌入到X、Y和Θ的三維循環中,因此總的周期數為9+(9*X*Y*Θ),即在每個處理塊中只包括9個這樣的周期:延遲+(9個周期*64個像素*64個像素*64位深度)。

盡管FPGA中可以實現浮點運算單元,但它們能迅速消耗FPGA的資源,所以如果可以,最好謹慎使用。主要依靠浮點運算的算法最好轉換成定點運算,這樣你既可利用用“模塊浮點”方法,又可通過定點的方法設計整個系統。然后,通過對比實際輸出與原始的全浮點運算的軟件實現來確定轉換精度。在霍爾算法的例子中,14b+7b的定點分辨率與全浮點的結果完全相同。

2確定資源

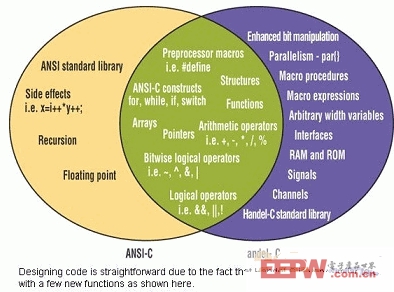

在接下來的設計中,需要對每個處理部分的時鐘周期計數。通常,每個時鐘周期可以完成二到三個運算,然后確定所需的FPGA資源以適應代碼。可以在多個FPGA中分段運行代碼來獲得更高的計算能力。這些解決方案的拓展非常容易,只要使用所需的多個FPGA(最多5個),系統將自動檢測它們。在該例子中,設計是基于處理塊的。這些塊按順序被發送給每個FPGA,或者從每個FPGA收集起來(其邏輯是代碼的一部分)。一個FPGA的加速比例可以達到37:1,而10個FPGA(每兩個電路板上有5個)可以達到370:1。對設計進行編碼相對簡單,因為設計主要由C語言完成,除了一些需要特殊Handel-C指令的新功能。這些新指令包括:增強位操作、并行處理、宏操作和公式、任意寬度的變量、FPGA存儲器接口、RAM和ROM類型、信號(代表硬件中的信號線)以及通道(在代碼并行分支或時鐘域之間通信)。工具條中的“代碼轉換”可以完成C和Handel-C的樣本轉換。

3對環境的仿真

再下一步是建立仿真環境,并在其中測試和優化硬件代碼。仿真環境提供了完整的bit-true/cycle-true仿真,并對FPGA的實現進行可靠的模擬。利用設計輸出與C軟件仿真輸出的比較來測試精度,同樣也可得到FPGA處理器上真實運行速度的報告。通常,進行結構塊仿真有助于找到設計中的問題,因為這些塊在重組后可以確定總體的運行效果。可在仿真過程中做進一步的調整,如利用流水線在每個時鐘周期內進行單輸入單輸出的測試,或將處理過程細分到更多的并行數據流中直到FPGA的資源利用率達到100%。此外,在硬件編譯時也能發現算法的最慢點并對其優化,在FPGA甚至板子之間分割算法還可以獲得額外的速度。利用軟件,進一步調整可獲得更好的性能。然而,精確調整帶來的性能增益卻會下降。通過簡單的增加FPGA非常具有成本效益。并不需要使設計完美化,因為基于這些結果的設計可以在任何時候進行快速的仿真和優化。一旦仿真完成,就可以將設計編譯到硬件里并激活數據流管理(DSM),以便將數據流送到FPGA處理器板而不是仿真器中。

訪問TI網站,獲取最新技術信息全面了解德州儀器(TI)的處理器電源參考設計:交叉參考搜索、應用手冊、工具和軟件、方框圖參考設計、模擬eLAB。

評論