基于Spartan-3A DSP的安全視頻系統分析

利用FPGA加速器模塊增壓

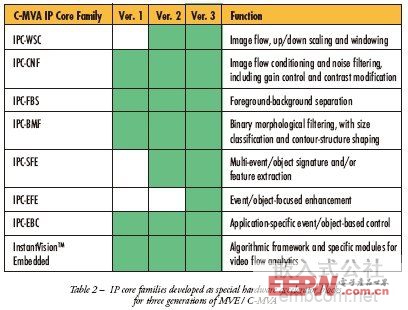

為真正發揮FPGA視頻分析系統的全面潛力,我們需要將視頻加速引擎集成到嵌入式系統中。我們預見到幾個性能瓶頸,因此設計小組開始采用VHDL進行一組加速器的早期開發。作為賽靈思ISE設計套件和嵌入式開發套件(EDK)的一部分,代碼剖析器幫助我們進一步確定性能瓶頸并開發設計所需要的所有加速器模塊。表2提供了系列IP內核的全面列表。

表2:為第三代MVE / C-MVA開發的專用硬件加速模塊IP內核系列。

與其他開發小組一樣,我們的開發小組也分別由不同的硬件和軟件開發人員組成。對于維持開發人員的生產力以保證項目的成功來說,在這兩個設計領域之間保留足夠的抽象非常關鍵。我們利用Xilinx Platform. Studio中的Create IPWizard來改進這一任務,為硬件加速模塊生成RTL模塊和軟件驅動文件。這些模塊包括訪問寄存器所需要的接口邏輯、嵌入式系統中的DMA邏輯和FIFO。一旦利用模塊創建了RTL,我們就將其放到嵌入IP目錄中,設計人員可根據需求進一步修改。

我們的IP內核開發流程包括一個通用的標準外設模塊開發流程,用于基于PLB46MPMC-OPB的回傳。這些外設包括單端和多I/O原型(SIMO、MIMO、MISO模型),支持我們為要求苛刻的圖像流處理算法靈活創造多線程協處理器流水線。在設計和定制不同分析引擎的過程中,通過近乎任意次序對IP內核進行組合和配置,我們達到了這方面的要求。

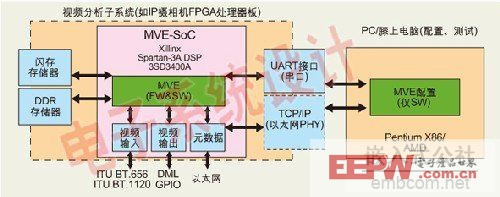

MVE分析引擎由InstantVision嵌入式軟件模塊以及構成C-MVA分析協處理器的硬件加速器組成。我們在一片Xilinx Spartan-3A-DSP 3400AFPGA中實現了MVE的原型,并創建了SoC參考設計。其中包括所有通信和數據流所需要的I/O功能(參考圖2了解完整的硬件固件框圖)。這一完整的SoC參考設計使用了91%的邏輯片資源、81%的塊RAM和32%的DSP邏輯片,不僅包含MVE分析引擎,還包括所有支持I/O模塊。

圖5:完整的硬件-固件-軟件參考設計。

單就MVE分析引擎來說(不包括MPMC-PLB主干和專用I/O組件),它僅使用了46%的邏輯片、44%的塊RAM和23%的DSP邏輯片,因此可以將其移植到成本更低的Spartan3A-DSP 1800A FPGA器件。

在單個時鐘周期內,我們設計的CMVA協處理器中所有IP內核可以完成所有相關處理。這一功能與異步FSL接口相結合,系統集成商能夠利用來自系統其它部分的不同時鐘域來驅動C-MVA協處理器。這樣做可以讓C-MVA在較低的像素時鐘頻率中運行,同時利用更高頻率的內部系統時鐘來驅動主干(backbone),從而在保證系統性能要求的同時大大降低功耗。

定制、封裝和系統集成

為驗證并進一步開發這一系統,我們創建了一個包括所有軟件層在內的安全/監控應用,允許用戶在系統的不同層面快速集成我們的產品(參見側欄)。完整SoC設計在單個參考設計中包括硬件IP內核、固件和軟件,請見圖4。

我們可在硬件、固件和軟件組件等不同層次進行靈活定制以組成系統集成。服務器級的定制包括FPGA中的可定制SoC設計,而在客戶(配置)一級,則可在WIN32 或 .Net API層進行修改。這種架構使我們及客戶可快速實現不同配置和測試接口的原型。

用戶可以在UART或TCP/IP上實現客戶-服務器(C/S)通信,從而提供靈活的配置管理、性能精細調整、狀態監控和固件升級。

盡管剛剛完成第二代產品,但我們已經開始考慮第三代產品的要求。根據在這一項目中取得的經驗,我們在新一代產品中會著重考慮賽靈思的FPGA器件,特別是賽靈思公司正在致力于利用最先進的工藝技術推出更可靠更先進的新器件和DSP功能。

評論