基于FPGA與DSP導引頭信號處理中FPGA設計

3.1.2跨R寸鐘域的處理

現代IC與FPGA設計巾使用的綜合工具可以保證設計能滿足每個數字電路觸發器對建立與保持時間的要求。然而,異步信號卻給軟件提出了難題。對新的時鐘域米說.從其它時鐘域傳柬的信號是異步的。大多數綜合丁具在判定算步信號是否滿足觸發器時序要求時遇到了麻煩。因為它們不能確定觸發器處于非穩態的時間,所以它們也就不能確定從一個觸發器通過組合邏輯到達下一個觸發器的總延遲時間。所以,最好的辦法是使用一些電路來減輕異步信號的影響。

同步措施歸納起來主要有兩方面,

1)對于跨越時鐘域控制信號,用同步器來實現同步;

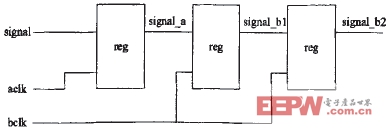

為了使同步。工作能正常進行,從某個時鐘域傳來的信號應先通過原時鐘域上的一個觸發器,然后不經過兩個時鐘域間的任何組合邏輯,直接進入同步器的第一個觸發器中(圖3)。這一要求非常重要,因為同步器的第一級觸發器對組合邏輯所產生的毛刺非常敏感。如果一個足夠長的信號毛刺正好滿足建立一保持時問的要求,則同步器的第一級觸發器會將其放行,給新時鐘域的后續邏輯送出一個虛假的信號。

圖3同步器示意

一個經同步后的信號在兩個時鐘沿以后就成為新時鐘域中的有效信號。信號的延遲是新時鐘域中的一到兩個時鐘周期。一種粗略的估算方法是同步器電路在新時鐘域中造成兩個時鐘周期的延遲,設計者需要考慮同步延遲將對跨時鐘域的信號時序造成的影響。

2)對于跨越時鐘域的數據總線,要通過FIFO或RAM達到同步的目的。

數據在時鐘域之間的傳遞是多個隨機變化的控制信號在時鐘域之間傳遞的一種實例。這種情況下,用同步器米處理同步問題往往不能收到滿意的效果,因為多位數據的變化將會使同步器的采樣錯誤率大大增加。常用的數據同步方法有兩種:一種是用握手信號;另一種是用FIFO,一個時鐘存數據。另一個時鐘取數據。

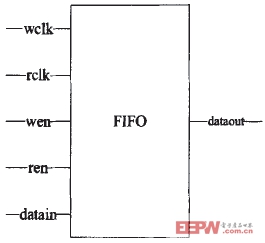

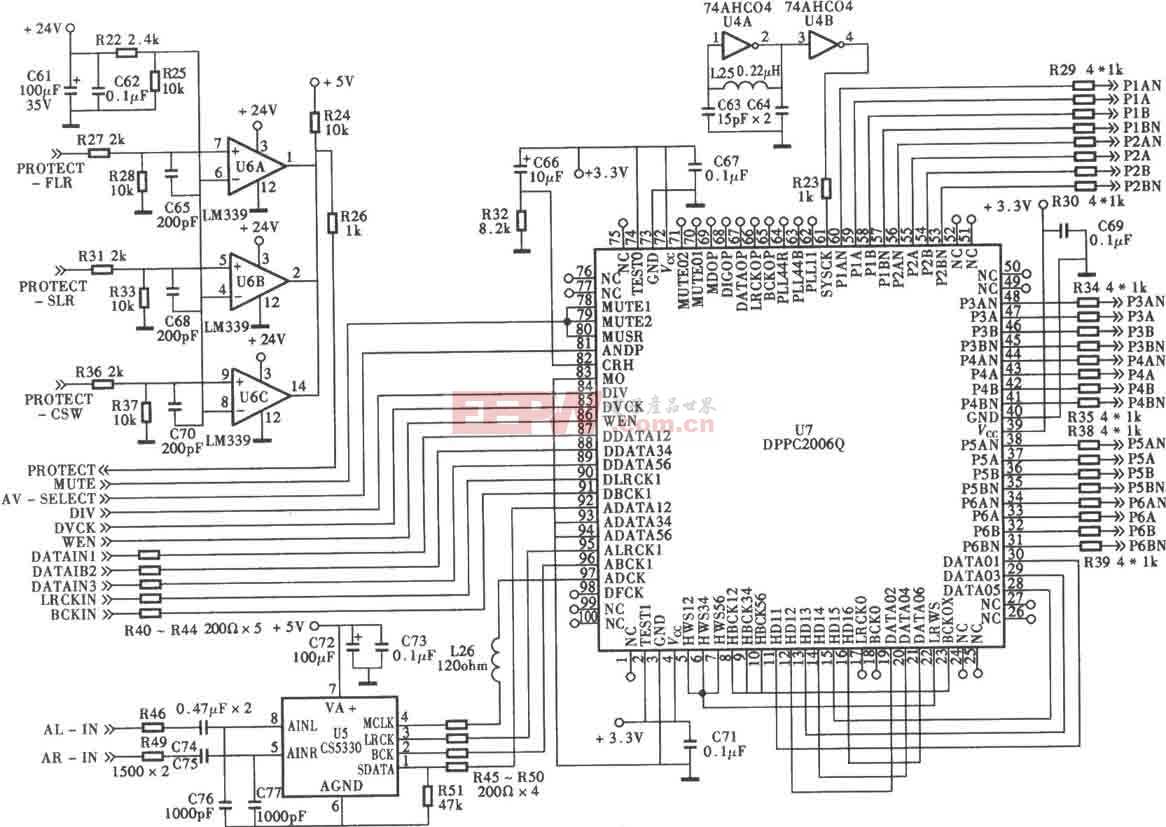

時鐘域之間的數據傳輸用得最多的是FIFO,采用Xilinx自帶的FIFO核來實現比較簡單方便,圖4足Xilinx提供的FIFO核的一個簡單的示意圖.wclk為寫時鐘,rclk為讀時鐘,FIFO深度通過讀寫使能wen和ren控制。

圖4 FIFO核示意圖

實際應用過程中,DSP和FPGA程序設計往往是由不同的設計人員分工完成,在最后系統聯調時,這兩者之間的數據傳輸經常占用大量的調試時間,成為約束工程進度的關鍵兇素。因此,DSP與FPGA間接口和傳輸方式的選擇與設計,是系統設計中必須要考惑的問題。

導引頭信號處理的一個特點是,FPGA要傳輸給DSP的數據比較多,需要傳遞幅度信息,和差支路數據等十幾組數據.每組數據長度在512~2K,而且讀取速度要求也比較高,一般要求百兆以上的讀取頻率。經過工程實踐表明,采用通過EDMA通道同步讀取FIFO的方式實現通信是非常有效的方法。但是接口處的FIFO比較多,而且讀取速度有比較高,這勢必導致FPGA內部對接口處資源的競爭,甚至會導致時序的不滿足。在實際工程調試中表現在DSP接收到的數據亂序,周期循環甚至亂碼。

要解決好FPGA和DSP的數據交互問題,要注意以下兩個方面。

3.2.1 三態門的設計

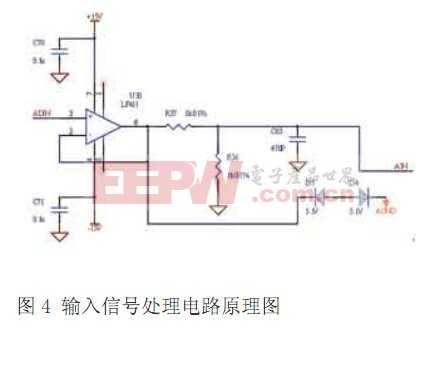

在本設計中,DSP和FPGA的互連采用了總線連接的方式,數據交互是通過一個32位的雙向數據總線來完成的,而要實現雙向總線,就需要使用FPGA構造三態總線了,使用三態緩沖器實現高、低電平和高阻三個狀態。

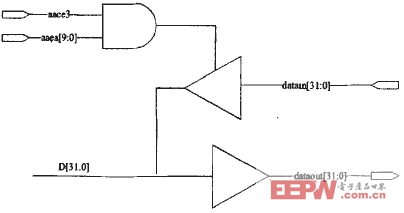

圖5雙向數據總線的三態門設計

本設計當中,FPGA給DSP發中斷信號,DSP在中斷信號到來時,根據系統要求,將不同的控制字寫入數據總線,然后通過數據總線從FPGA中不同的FIFO中讀取數據,這一切都通過DSP在地址線上給出不同的地址來完成。為了合理分配總線的使用,設計當中使用這樣的策略:利用片選信號aace3,地址aaea[9:0]作為三態緩沖器的控制信號,由于DSP對FPGA的讀寫地址都不同,當片選信號aace3有效時,FPGA根據地址來確定湊寫方式以及讀寫那些信息,否則置為高阻態,這樣就避免了可能產生的的總線阻塞現象,使DSP和FPGA之間的數據交互能夠順利進行,示意圖如圖5所示。

3.2.2 加有效的時序約束

由于接口FIFO比較多,為了合理分配FPGA內部接口處的資源,滿足系統的時序要求,需要加必要的時序約束。因為本設計采用Xilinx公司芯片,所以需要加偏移約束2。

偏置約束可以優化以下時延路徑:從輸入管腳到同步元件偏置輸入;從同步元件到輸出管腳偏置輸出。為了確保芯片數據采樣可靠和下級芯片之間正確交換數據,需要約束外部時鐘和數據輸入輸出引腳問的時序關系。偏置約束的內容告訴綜合器,布線器輸入數據到達的時刻或者輸出數據穩定的時刻,從而保證與下一級電路的時序關系。更多關于約束的內容請參閱文獻。

4 結束語

FPGA+DSP是同前導引頭信號處理器中運用的最廣泛的系統組成形式,對速度以及靈活性的要求都能夠很好的滿足,文中所涉及到的跨時鐘域設計以及數據接口方面的問題是這樣的系統中FPGA設計存在的關鍵技術,文中提出了詳實的解決方法,而且工程應用已經證明了其有效性。

本文作者創新點:依據工程實踐經驗,總結了在FPGA+DSP結構的雷達導引頭信號處理中FPGA的關鍵問題,并提出了詳細的解決方案,并得到了工程驗證。

評論