基于ADSP-TS101S的雷達信號處理系統的設計

(4) 相參積累

可按矢量相加方式積累,積累幀數為16個;本設計采取滑窗方式保存本幀周期和前15個幀周期的視頻數據:積累后除以16就可以取得平均值。DSP4在做完相參積累后就將處理過的數據送往MTD板做后續處理。

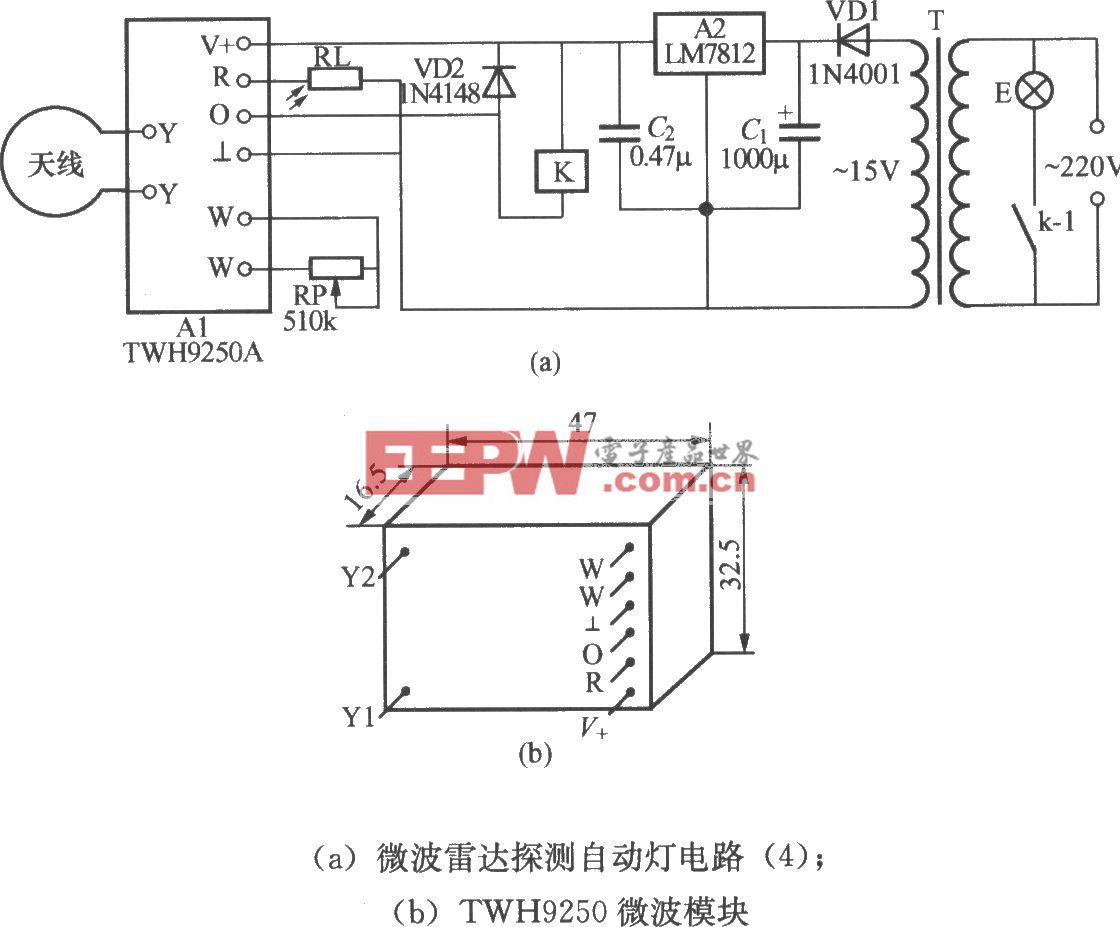

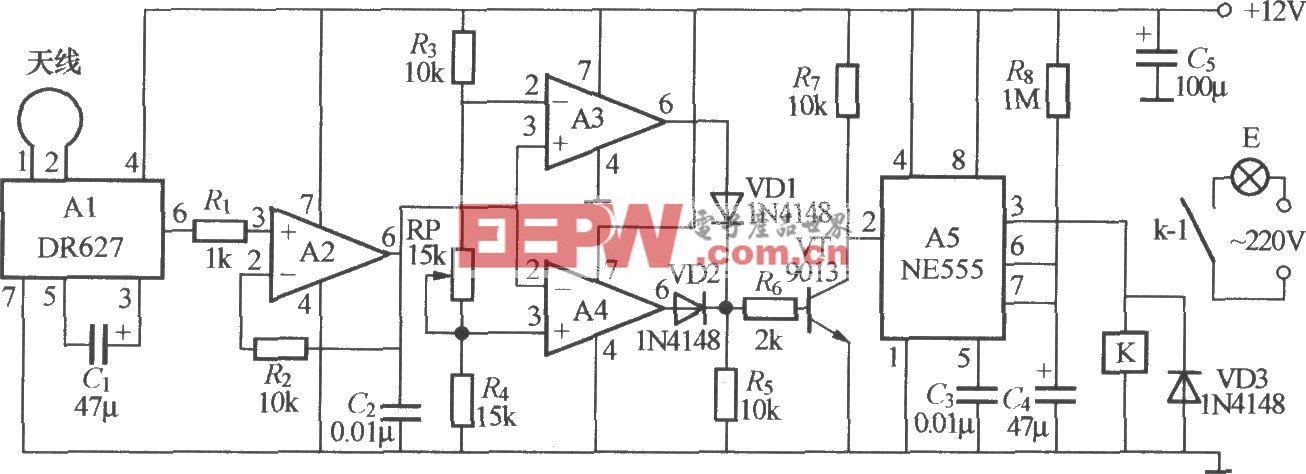

1.4 MTD板

MTD板實現的主要功能包括MTD處理、CFAR處理和非相參積累。

(1) MTD處理

MTD處理主要包括8點FFT程序和求模兩部分。圖3所示是其結構原理圖,其中求模可采用如下近似公式:

該算法可在DSP1中完成,處理結果送入DSP2。

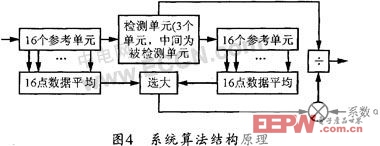

(2) CFAR處理

本系統中采用的算法框圖如圖4所示,CFAR處理的參考單元數N為35,前后各16個距離單元。

該算法在DSP2中完成后,將處理結果送到DSP3。

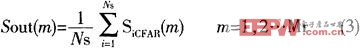

(3) 非相參積累

常用的非相參積累有單極點積累器、雙極點積累器、滑窗積累平均積累等,本文采用簡單的滑窗平均積累,其中Ns=8,Mr為總點數。那么:

該算法以及下面模塊中的前半部分均在DSP3中實現。

(4) 輸出模塊

通過輸出模塊先完成浮點轉定點,再乘以適當系數將數據范圍壓縮到10位,然后把大于零的振幅數據輸出到D/A的視頻數據,并用前幀同步作為中斷,利用DSP的DMA0來將數據傳至FPCA,再將FPGA鎖存后的lO位視頻信號輸出到DAC。DAC選用具有10位有效數據位、125MSPS轉換速率的高速器件AD9750,將數字信號轉換為模擬信號后,可由OPA692F運算放大器驅動,并由視頻電纜輸出,以分別接到主機和顯示設備。

2 系統設計注意事項

2.1 時鐘

由于本系統是由多片ADSP-TS101組成的系統,所以由40 MHz晶振產生的時鐘信號不能直接接到各DSP和FPGA,而應該通過驅動后再接到各DSP,且時鐘信號到各DSP的距離應該盡可能接近。本系統中采用的時鐘驅動芯片為IDT49FCT805。另外,在PCB布線時,應該將時鐘信號盡量布在地層,并對其加以保護。

2.2 電源

ADSP-TS101有三個電源,其中數字3.3 V用于I/O供電;數字1.2 V用于DSP內核供電;模擬1.2 V為內部鎖相環和倍頻電路供電。運行時要求數字3.3 V和數字1.2 V應同時上電。若無法嚴格同步,則應保證內核電源1.2 V先上電,I/O電源3.3 V后上電。本系統在數字3.3V輸入端并聯了一個大電容,而在數字1.2V輸入端并聯了一個小電容,其目的就是為了保證3.3V充電時間大于1.2V充電時間,以解決上述問題。系統用主機送來的5 V電壓經過TPS54350得到3.3 V和1.2 V的電壓。各片DSP的數字1.2 V電源各由一片TPS54350供給。6片DSP內部模擬1.2 V則由同一DSP芯片的VDD (1.2 V)經濾波網絡后提供。FPGA的I/O電源為3.3 V,可由電源轉換后直接使用,其2.5 V核電壓應該單獨由一片TPS54350來輸出供電。

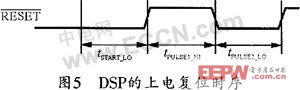

2.3 ADSP—TS101S的復位

TigerSHARC DSP的上電復位較為特殊,在設計時應充分引起重視。該DSP的上電復位波形要求如圖5所示。這里應當注意的是,tstart_LO在供電穩定之后,還必須大于1 ms才能進行操作:而tpulsel_HI則必須大于50個系統時鐘周期且小于100個系統時鐘周期;tpulse2_LO必須大于100個系統時鐘周期。

該DSP上電后正常復位時,低電平持續時間必須大于100個系統時鐘周期。本系統采用Altera公司的FPGA EPlK100來產生上電復位波形和時序控制。由于EPlK100需要一個配置芯片,而且它和DSP存在一個上電先后的問題。也就是說,在上電后,如果FPGA芯片在進行配置文件的讀入時,DSP上電仍未穩定,則應充分延長tstart_LO的低電平時間,以避免上電未穩定而FPGA上的波形已經結束。因此,應保證DSP上電穩定先于FPGA芯片配置文件的讀入,此問題在系統設計時應予以充分重視,否則DSP將無法正常工作。

3 結束語

本文詳細地介紹了雷達信號處理的各種算法在ADSP-TS101中的實現方法。該系統充分利用了ADSP-TS101S高速的運算能力及數據吞吐量。文中討論了DSP應用過程中的時鐘設計、電源設計和DSP復位問題,因而具有一定的工程指導意義。實踐表明,由ADSP—TS101S構成的系統硬件結構簡單,軟件編寫方便,而且成本較低。目前,該系統已成功應用于某雷達信號處理機中。

評論