基于DSP的合成孔徑雷達成像系統逆存儲轉置器設計

5.軟件設計與實現

TMS320C6415是面向C結構的DSP芯片,支持標準C/C++編程,其開發工具Code Composer Studio(CCS2.21)內嵌C編譯器的編譯效率可達匯編的85%。另外,C編程可提高DSP程序的可維護性、可移植性、可繼承性,便于縮短軟件開發周期,因此本DSP程序選擇采用C語言編寫。

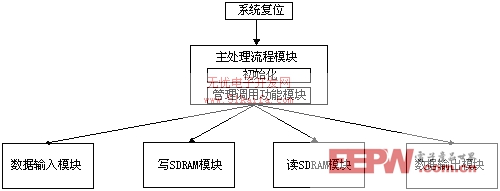

圖3 程序層次結構和模塊劃分

5.1軟件模塊劃分

軟件層次結構和模塊劃分如圖3所示。DSP軟件的主要部分是底層的四個功能模塊,這四個功能模塊分別完成以下操作:1. 從輸入FIFO中讀取兩條方位線數據(每條方位線2048點,每點數據類型為短整型)到DSP內存中;2. 將讀入的數據按順序存儲到SDRAM中;3. 把SDRAM中的數據沿距離線順序讀到DSP內存中,即完成轉置操作;4. 把轉置后的數據送至輸出FIFO。

5.2軟件各模塊間關系

l 上電初始化模塊:在DSP上電后,完成與硬件工作有關的各控制寄存器的初始化,以及與軟件工作有關的各內部變量和存儲區的初始化;

l 主處理模塊:調用其它功能模塊,完成整個逆存儲轉置流程;

l 數據輸入模塊:受主處理模塊調用,利用EDMA完成數據輸入;

l 寫SDRAM模塊:受主處理模塊調用,利用EDMA完成數據寫操作;

l 讀SDRAM模塊:受主處理模塊調用,利用EDMA完成數據讀操作;

l 數據輸出模塊:受主處理模塊調用,利用EDMA完成數據輸出。

5.3 C6415的EDMA控制寄存器

EDMA是C621x/671x/641x特有的數據存取方式。在C621x/671x/641x中,EDMA控制寄存器負責片內二級存儲器與其它外設之間的數據傳輸。EDMA控制寄存器和DMA控制寄存器在結構上有很大不同。其增強之處包括:

l 提供了64個傳輸通道;

l 通道間優先級可設置;

l 支持不同結構數據傳輸的鏈接。

EDMA控制寄存器主要由事件(中斷)處理寄存器、事件編碼器、參數RAM以及硬件地址發生器構成。其中,事件(中斷)處理寄存器負責對EDMA事件進行捕獲。一個事件相當于一個同步信號,由它觸發一個EDMA通道開始數據傳輸。如果多個事件同時發生,則由事件編碼器對它們進行分辨,將同時發生的事件進行排序,并決定事件的處理順序。EDMA的參數RAM中存放了有關的傳輸參數,這些參數會被送往硬件地址發生器,進而產生讀寫操作所需的地址。

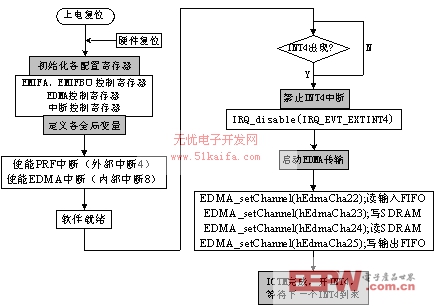

5.4 ICTM軟件設計流程

圖4 ICTM軟件設計流程

ICTM模塊軟件設計流程可用圖4來表示。首先完成上電復位,初始化EMIFA和EMIFB配置寄存器、中斷控制寄存器和EDMA控制寄存器,之后在主程序中完成各常量和變量的定義及初始化。完成上述初始化定義后就可以使能外部中斷控制寄存器和EDMA控制寄存器,等待外部中斷INT4的觸發。INT4的觸發源來自脈沖PRF,該脈沖的到來說明兩條待輸入的方位線數據已送至輸入FIFO,此時CPU可以將這兩條方位線數據讀到DSP內存,并送至SDRAM的相應存儲區。

由于輸入/輸出數據結構相對簡單,讀輸入FIFO、寫SDRAM、讀SDRAM以及寫輸出FIFO四個過程可以采用“EDMA鏈(EDMA Chain)”的方式進行。即第一個EDMA傳輸完成后,緊接著啟動第二個EDMA傳輸,直到最后一個EDMA傳輸完成,這樣可以在不受CPU干預的情況下完成數據的搬移,有利于提高數據傳輸效率。

5.5 軟件并行設計問題

由于EDMA不受CPU干預,因此在使用EDMA傳輸數據的同時,CPU可并行執行其它指令,這樣可極大提高代碼的執行效率。舉例如下:

if(EDMA_intTest(22))

{

*ifoeoff=0;

EDMA_intClear(22);

EDMA_setChannel(hEdmaCha25);// trigger EDMA to reading data from SDRAM

#pragma MUST_ITERATE(32,,8);

for(i=0;i {

headwriteaddr[ i]=inputa[ i];

}

WORD_ALIGNED(inputb);

WORD_ALIGNED(inputc);

WORD_ALIGNED(inputa);

#pragma MUST_ITERATE(64,,8);

for(i=0;i {

inputb[ i]=inputa[2*i+64];

inputc[ i]=inputa[2*i+65];

}

}

其中EDMA_setChannel(hEdmaCha25)語句用來啟動EDMA25通道的傳輸,完成從SDRAM讀取轉置數據的任務。EDMA在進行數據傳輸的同時,CPU則繼續執行之后的三條語句headwriteaddr[ i]=inputa[ i]、inputc[ i]=inputa[2*i+65]、inputb[ i]=inputa[2*i+64],直到EDMA傳輸完成并發出中斷,CPU才響應EDMA中斷。

顯然,采用上述并行處理的方式,CPU工作周期得到充分利用,提高了代碼的執行效率,有利于滿足系統的實時性要求。

6.結束語

逆存儲轉置器(ICTM)是合成孔徑雷達(SAR)實時成像處理系統的一個重要模塊。本文選擇TI的一款高性能定點DSP芯片TMS320C6415為核心處理器,兩條大容量SDRAM作為外部存儲器,實現輸入數據的逆存儲轉置操作。軟件編程采用并行處理方式,提高了代碼執行效率。單板測試和系統聯調表明,設計的逆存儲轉置器滿足各項性能指標,已通過項目組驗收,即將投入實際應用。

評論