基于DSP的MP3解碼系統(tǒng)設(shè)計(jì)方案

基于DSP實(shí)現(xiàn)MP3解碼系統(tǒng)的設(shè)計(jì),采用高性能的立體聲音頻Codec芯片TLV320A IC23 作為音頻信號數(shù)模轉(zhuǎn)換,DSP的兩個(gè)McBSP與其連接,分別作為配置接口和音頻數(shù)字接口,配置接口設(shè)置為SP I模式。USB與DSP接口實(shí)現(xiàn)MP3數(shù)據(jù)流與PC機(jī)之間的上傳與下載,存取MP3文件方便,存儲MP3文件的媒介選取大容量的存儲設(shè)備CF卡,系統(tǒng)選用可編程邏輯器件CPLD控制USB及CF卡的讀寫和片選。實(shí)驗(yàn)證明該系統(tǒng)可以高質(zhì)量完成MP3解碼、播放。

本文引用地址:http://www.104case.com/article/257314.htm隨著數(shù)字視頻和圖像處理的發(fā)展,數(shù)字音頻技術(shù)也正在提高,尤其是以ISO / IEC 為基礎(chǔ)的MPEG技術(shù)。MP3是MPEG Audio LayerⅢ的縮寫,它是Hi - Fi級音頻壓縮的國際標(biāo)準(zhǔn)。目前,市場上的MP3解碼基本上都是采用專用芯片解碼,采用專用芯片解碼體積大,支持的音頻格式有限。我們采用在DSP芯片上用C語言進(jìn)行軟解碼,軟解碼比較靈活,可移植性好,易于升級,解碼質(zhì)量可通過軟件參數(shù)設(shè)定,通用性好。

硬件系統(tǒng)結(jié)構(gòu)

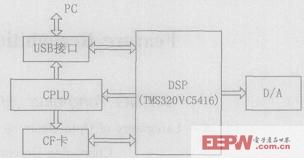

DSP的MP3解碼系統(tǒng)硬件框圖如圖1所示,我們采用了低功耗的DSP芯片TMS32VC5416進(jìn)行軟件解碼,32M的CF卡作為存儲MP3文件的媒介,USB接口作為與PC機(jī)進(jìn)行通訊接口,傳輸數(shù)據(jù)速度快,可以在PC機(jī)下載、上傳MP3,可編程邏輯器件CPLD (選用EPM7128SL84)用于產(chǎn)生CF卡與USB 接口芯片的片選以及控制其讀寫。

TMS320VC5416定點(diǎn)DSP

TI公司的TMS320VC5416 定點(diǎn)運(yùn)算數(shù)字信號處理器(DSP) ,其功耗低,性能高,內(nèi)部采用一種改進(jìn)型的哈佛總線結(jié)構(gòu):一條程序總線,3條數(shù)據(jù)總線,數(shù)據(jù)總線寬度為16位。分開的數(shù)據(jù)和指令空間使該芯片具有高度的并行操作能力,在單周期內(nèi)允許指令和數(shù)據(jù)同時(shí)存取,再加上其高度優(yōu)化的指令集,使得該芯片具有很高的運(yùn)算速度,最高可達(dá)160MIPS。

圖1 系統(tǒng)的硬件框圖

音頻傳輸、播放系統(tǒng)

TLV320A IC23介紹

D /A采用TLV320A IC23 芯片,TLV320AIC23 (以下簡稱AIC23)是一款高性能的立體聲音頻Codec芯片,內(nèi)置耳機(jī)輸出放大器,支持MIC和LINE IN兩種輸入方式(二選一) ,且對輸入和輸出都具有可編程增益調(diào)節(jié)。AIC23 的模數(shù)轉(zhuǎn)換(ADCs) 和數(shù)模轉(zhuǎn)換(DACs)部件高度集成在芯片內(nèi)部,采用了先進(jìn)的Sigma-delta過采樣技術(shù),可以在8K到96K的頻率范圍內(nèi)20、24 bit和32 bit的采樣,ADC和DAC的輸出信噪比分別可以達(dá)到90dB 和100dB。與此同時(shí),AIC23還具有很低的能耗,回放模式下功率僅為23 mW,省電模式下更是小于15uW。由于具有上述優(yōu)點(diǎn),使得AIC23是一款非常理想的音頻模擬I/O器件。

AIC23與DSP的數(shù)字音頻接口設(shè)計(jì)

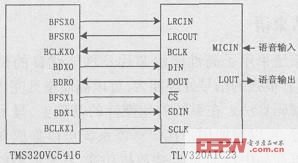

DSP與AIC23連接如圖2 所示,利用USB1. 1接口器件PDIUSBD12可編程的時(shí)鐘頻率輸出12M作為立體聲音頻Codec芯片AIC23的時(shí)鐘輸入CLK12M。AIC23的配置接口支持IαC模式,也支持SPI模式,系統(tǒng)采用DSP的一個(gè)McBSP用SPI模式跟AIC23連接。

圖2 TLV320A IC23與DSP連接圖

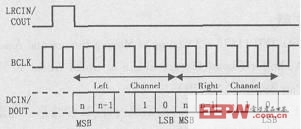

DSP配置為主模式,AIC23 配置為從模式。AIC23 輸出串行數(shù)據(jù),DSP的MCBSP串口6個(gè)引腳使數(shù)據(jù)通路和控制通路與AIC23 相連。數(shù)據(jù)由BDX0、BDR0 傳輸,同步信號的控制由BFSX0、BFSR0、BCLKX0 來實(shí)現(xiàn)。數(shù)字音頻接口采用DSP模式,該模式與TI公司DSP的MCBSP串口兼容,該模式時(shí)序如圖3。由圖知,在LRCIN /LRCOUT信號的下降沿開始進(jìn)行數(shù)據(jù)的傳輸,先左聲道數(shù)據(jù)傳輸,然后右聲道數(shù)據(jù)傳輸。

圖3 A IC23的DSP模式時(shí)序

DSP需要處理來自和發(fā)向AIC23的數(shù)據(jù),從而達(dá)到采集和播放聲音。McBSP與CPU 通信用DMA 方式,通過DMA 收到或發(fā)送完一組單元,再給CPU 中斷。采用DMA的方式,即串口每發(fā)送或接收到一個(gè)單元,都會自動觸發(fā)DMA將其搬送到一個(gè)內(nèi)部的Buffer,等Buffer滿了再通過中斷方式告訴CPU處理。在DMA的中斷服務(wù)程序中為了可靠可以把這個(gè)Buffer的數(shù)據(jù)再拷貝到另一個(gè)待處理的空間,即兩級Buffer,然后置標(biāo)志位,CPU在主程序中查詢標(biāo)志位然后作出相應(yīng)的處理。DMA 操作的Buffer可以通過寄存器配置。

評論