一種基于FPGA+ARM架構HDLC協議控制器設計

本文引用地址:http://www.104case.com/article/255887.htm

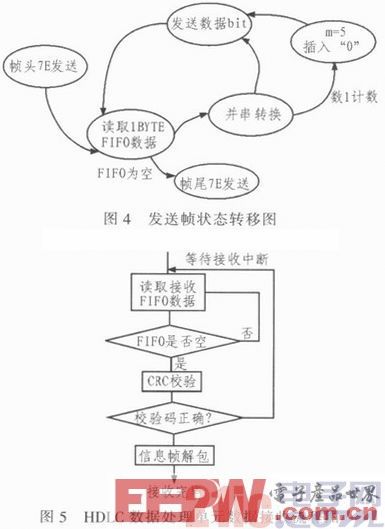

在發送端,接收到ARM啟動發送指令后,發送相應個數幀頭0x7E,然后將數據從發送FIFO中取出,進行并串轉換,在根據設置的時鐘TCLK的下降沿,逐位發送數據到Tx線路上,并且在連續發送了5個比特“1”后,自動插入比特“0”,發送結束后發送相應個數幀尾0x7E,結束該次發送。發送幀狀態轉移圖如圖4所示。

2.3 HDLC數據處理單元

HDLC數據處理單元主要完成信息的幀的CRC校驗和打包解包任務,其處理芯片采用意法半導體的STM32F103系列ARM芯片,該芯片具有開發簡單靈活,成本較低的優勢。數據處理單元對數據的處理同樣包括接收和發送兩部分,以接收為例,具體工作流程圖如圖5所示。

當進入接收中斷進程時,首先讀空接收FIFO,其中最后兩次讀出的數據為該幀信息的CRC校驗碼,利用該校驗碼進行CRC校驗,校驗采用CRC-16-CCITT標準,生成r取值為16,其生成多項式為:C(x)=x16+x12+x2+1傳統CRC校驗是對消息逐位處理,對于ARM來說,這樣效率是很低的。為了提高時間效率,通常的思想是以空間換時間。考慮到內循環只與當前的消息字節和crc_reg的低字節有關,針對crc_reg低字節建立數表進行查詢相應的CRC校驗碼,最終循環完畢如果沒有差錯發生則結果應為0。

發送單元與接收單元類似,為其逆過程,首先將信息按約定幀格式打包,然后進行CRC校驗,將校驗碼放入信息幀的最后2個字節,并將該信息幀通過數據總線存入FPGA的發送FIFO中,最后寫入發送標志字,啟動FPGA發送傳輸控制邏輯。

3 驗證及結果

為完成設計,首先采用ModelSim進行仿真驗證,如圖6所示通過激勵文件生成ARM與FPCA的讀寫時序,給出符合HDLC幀格式的一組數據寫入FPGA發送FIFO,并啟動發送,在激勵文件中將RX/RCLK與TX/TCLK短接,形成回環,FPGA根據協議控制器接收到數據,并將數據存入接收FIFO,完成驗證。其邏輯時序滿足HDLC協議幀格式和通信時序要求。

最后按照設計要求將設計好的HDLC通信協議控制器加載至FPGA與ARM上,并與串口通信卡BST23109進行回環測試,該卡能夠實現串口同步模式,通信滿足HDLC協議要求。試驗結果表明在5 m通信距離內,波特率可達2 Mb/s,誤碼率為10-8。

4 結論

文中針對飛行模擬裝置中HDLC協議的應用需求開展了HDLC協議控制器的設計,文中首先介紹了HDLC協議的相關內容,然后重點介紹了HDLC協議控制器軟硬件實現,詳細給出于HDLC協議控制器的沒計實現過程。通過仿真和實測試驗表明在5m通信距離內,波特率可達2Mb/s,誤碼率為10-8。在該飛行模擬裝置交付使用過程中,該控制器功能完整,能夠很好地滿足各項指標的技術要求。

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論