FPGA電路設計: 如何應對電源相關問題的挑戰

引言

在設計可編程門陣列(FPGA)電路時,必須極端重視電源問題,從而使最終產品能在所有可能的條件下無缺陷工作并處于最優狀態。FPGA 電路電源有兩項需考慮的問題: FPGA 電路上電要求和電路功耗分析。這篇文章針對這兩方面的要求,討論您可能遇到的問題,以及解決方案。

目前FPGA電路設計所面臨的問題

FPGA電路通常需要多路電源輸入。為優化開機時的電流拖曳,防止鎖死和永久性的電路損壞,同時也為了防止開機接通時的毛刺干擾和降低開機接通的功耗,這些電源輸入必須具有精確的上電序列以及正確的電壓變化率。如何實現復雜多路供電的精確控制是FPGA電路設計驗證過程中的難點。此外,隨著項目的發展,FPGA電路設計指標通常會發生變化,靈活簡單的上電參數調整方式也是工程師在進行前期電路設計時所需要的。

在產品設計過程中,還需要測試各種工作條件下的FPGA電路功耗,捕獲大電流尖峰的精確輪廓,并帶有時戳,以確定尖峰出現的時間,從而確定設計必須提供的最大電源功耗。可能還需要為電源資源有限的產品(如電池供電設備)進行進一步功耗優化設計。

實例: 為 Xilinx Spartan-3 FPGA 設置上電規則并進行功耗分析

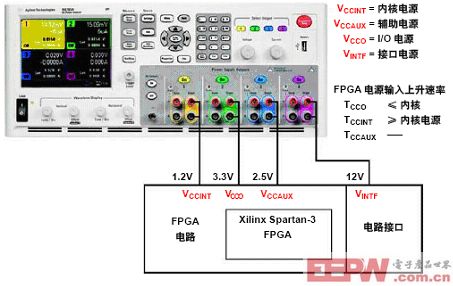

以Spartan-3系列FPGA為例,該FPGA電路需要四路供電,包括VCCINT(內核電源),VCCAUX(輔助電源),VCCO(I/O電源)和VINTF(接口電源)。其中VINTF用于為配置器件如NOR Flash PROM 或微控器供電的供電。為正確配置 FPGA,要在FPGA上電前 1毫秒開啟,這一上電間隔保證了配置器件已完成上電,并準備好向FPGA發送來自存儲器的配置。其他三路供電時序沒有嚴格要求,但如果VCCINT 在 VCCAUX 之前,或與其同時上電,FPGA將消耗過多的內核電流。這一過度的電流拖曳將更快降低電池壽命,并導致負責功率分配的設計人員選擇更大功率的調整器。

為驗證不同上電時序對FPGA電路消耗電流的影響,使用安捷倫 N6705A直流功耗分析儀按圖1所示與FPGA電路進行連接。

圖1 使用多路電源為FPGA電路供電時的連接和設置

評論