基于FPGA的交流電測量儀的設計

在電力調度自動化系統中,測量電壓和頻率是最重要的功能。如何快速、準確地采集顯得尤為重要。目前根據采集信號的不同,可分直流采樣和交流采樣兩種方式,直流采樣雖然設計簡單,但無法實現實時信號的采集;變送器的精度和穩定性對測量精度有很大影響,無法滿足電力系統實時性、可靠性的要求 。交流采樣法按照一定規律對被測信號的瞬時值進行實時采樣, 再按設計的算法進行數值處理, 從而獲得測量值。與直流采樣法相比更易獲得高精度、高穩定性的測量結果。由于FPGA運行速度快、內部程序并行運行,具有處理更復雜功能的能力,因此FPGA[1-3]和交流采樣相結合,可以滿足電力系統實時性、可靠性的要求。

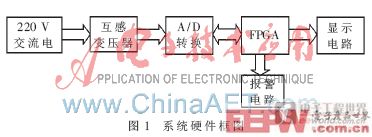

1 系統硬件電路組成

以日常照明所用的交流電(電壓為220 V,頻率為50 Hz)為測量對象,測量系統的組成電路主要包含供電、互感變壓器(TV)、A/D轉換電路以及FPGA、顯示電路和報警電路。測量系統框圖如圖1所示。

220 V交流電壓經過互感變壓器(TV)后的輸出電壓為-10 V~+10 V,滿足電壓芯片ADS7804輸入端的要求,通過ADS7804將輸入的模擬量轉換成數字量送到FPGA,得到量化電壓值。一方面在一個周期(0.02 s)內對電壓的采樣值采用計算均方根的方法計算出交流的有效值即電壓的大小;另一方面對量化的電壓值進行分析,計算出2個正弦波的時間,并算出頻率。通過顯示電路分別顯示電壓值和頻率值。如果電壓低于正常電壓的80%或達到正常電壓的120%,或者頻率低于49.00 Hz或高于51.00 Hz時,啟動報警電路。

1.2 ADS7804芯片

ADS7804芯片是12位A/D轉換器,以其較高的性能價格比在儀器儀表中得到廣泛的應用。ADS7804芯片內部含有采樣保持、電壓基準和時鐘等電路,可極大簡化用戶的電路設計,減少硬件開銷,并可提高系統的穩定性。該A/D轉換器采用逐次逼近式工作原理,單通道輸入,模擬輸入電壓的范圍為±10 V,采樣速率為100 kHz,可以完全滿足電力系統中50 Hz交流電的采樣需要。

ADS7804芯片的VIN(1腳)為輸入的模擬信號,輸入模擬量大小為-10 V~+10 V,6~18腳為輸入模擬信號轉換的數字量并行輸出口,用于將轉換的數字量輸出,CS(25腳)為片選信, R/C(24腳)為讀取結果/模數轉換控制信號,BUSY(26腳)用于指示轉換是否完成。讀取時首先將R/C腳電平變低;然后在CS腳輸人一個脈沖并在其下降沿啟動A/D轉換,此脈沖的寬度要求在40 ns之內;這時BUSY腳電平拉低表示正在進行轉換;在經過大約40 ns~6 μs以后,轉換完成,BUSY腳電平相應變高;再把R/C腳電平拉高,這樣,CS腳脈沖的下降沿即把轉換結果輸出到數據總線。

ADS7804芯片將模擬電壓轉換為數字量,以二進制的補碼輸出。該芯片電壓分辨率高達4.88 mV。

1.3 FPGA芯片

現場可編程門陣列(FPGA)作為專用集成電路(ASIC) 領域中的一種半定制電路而出現,是當今數字系統設計的主要硬件平臺,其主要特點就是完全由用戶通過軟件進行配置和編程,從而完成某種特定的功能。在修改和升級時,不需額外地改變PCB 電路板,只是在計算機上修改和更新程序,使硬件設計工作轉變為軟件開發工作,縮短了系統設計的周期,提高了實現的靈活性并降低了成本,因此得到廣泛的應用。

本設計中FPGA主要負責控制A/D采樣芯片ADS7804,并讀取轉換后的數字碼,然后按交流采樣原理進行實時計算,分別算出交流電壓的有效值、交流電壓的頻率,驅動顯示電路將電壓和頻率顯示出來,當出現電壓偏離正常值20%,或者頻率低于49 Hz或高于51 Hz時進行報警,供主處理器進行故障判斷。

本設計采用FPGA做處理器有以下優點:

(1)由于FPGA并行處理的特點,可同時運算多路模擬量,即多路交流量對應的各個模塊可以同時采樣計算,所以計算速度上有了質的飛躍;

(2)在FPGA 設計中,FPGA可以并行地處理采樣、計算、顯示、報警等模塊,大大提高了運行速度,并滿足電力系統實時性、可靠性的需要。

1.4 LED顯示

LED數碼顯示管有共陰極和共陽極兩種接線方法,本設計采用共陽極,低電平有效,其中abcdefg組成數碼管顯示,dp為小數點顯示。s1、s2、s3、s4、s5、s6、s7、s8分別為選擇端,當其為高電平時選擇相應的數碼管。本設計主要采用兩組顯示,其中s1、s2、s3、s4為第一組顯示,用于顯示電壓;s5、s6、s7、s8為第二組顯示,用于顯示頻率。例如要讓第一組第一個碼管顯示0時,其他數碼管燈滅,則abcdefg=0000001,dp為小數點位置0,s1=1,s2=0,s3=0,s4=0。

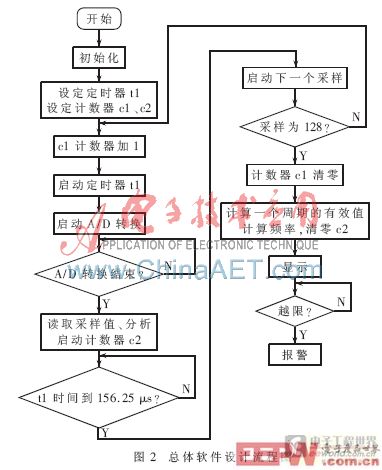

2 系統軟件設計

2.1 軟件設計流程

由離散化公式可知, 根據一個周期內不同時刻的電壓采樣值及采樣點數可計算出電壓的有效值[5]。為了提高計算精度,本設計在一個周期內采樣128個點用于計算有效值。同時通過對128個采樣點進行分析計算出頻率。

在實際設計時,FPGA晶振為40 MHz,用于準確定時,以確定每個采樣的間隔時間,從而準確地啟動A/D轉換,同時ADS7804芯片的轉換時間為10 μs左右,本采樣周期為156.25 μs,本設計完全滿足FPGA及時精確的采樣要求。

本軟件設計主要包括一個定時器t1、兩個計數器c1和c2,定時器t1用于確定采樣時間,控制采樣;計數器c1用于確定一個交流電周期共采樣128次,利用交流電采樣原理公式計算交流電一個周期內電壓的有效值;計數器c2用于計算頻率。通過正弦的規律,計算出3次從正值到負值或者3次從負值到正值這段時間(即2個周期內)采樣點的個數,通過采樣點的間隔時間,得出2個周期的時間,從而計算出頻率的大小。總體軟件設計流程圖如圖2所示。

評論