基于FDATool的FIR濾波器設計方法(一)

FIR濾波器根據輸入數據速率的不同可分為串行結構、半并行結構和全并行結構。串行結構的FIR濾波器是將并行數據串行輸入,所需的DSP資源較少,但是數據吞吐率較低;而全并行結構的FIR濾波器數據是并行輸入,濾波系數的個數就決定了所需DSP資源的個數,資源耗用較多,但是吞吐率可以做到很大。在大多數應用中,如無線數字中頻處理,所需數據吞吐率一般都較高,因此采用的是全并行結構的FIR濾波器。

本文引用地址:http://www.104case.com/article/249651.htm全并行FIR濾波器根據實現結構不同可分為:直接型(Transverse)、轉置型(Transpose)和脈動型(Systolic),這一節主要講解直接型FIR濾波器設計。

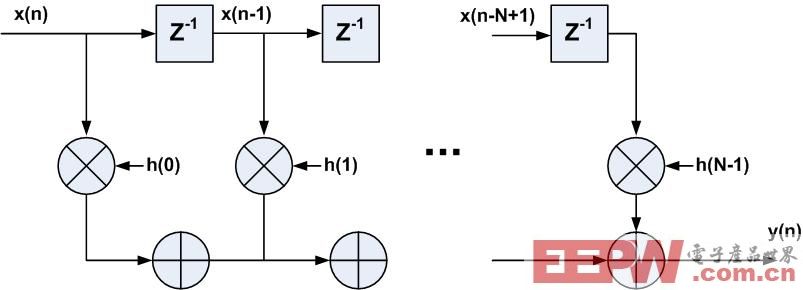

(一)直接型

直接型FIR濾波器在上一節中也有介紹,如圖1所示,數據x(n)移入并寄存,如果有11個抽頭,因此直接型FIR濾波器需要11個乘加模塊。

圖1

FPGA實現時,直接采用上圖中結構,不對中間數據寄存,則關鍵路徑是x(n)h(0)+x(n-1)h(1)…x(n-N+1)h(N-1),以階數10的FIR濾波器為例,如下為抽頭系數:

coe_0 = -1241

coe_1 = -650

coe_2 = 1300

coe_3 = 4739

coe_4 = 8126

coe_5 = 9544

coe_6 = 8126

coe_7 = 4739

coe_8 = 1300

coe_9 = -650

coe_10 = -1241

數據輸入時打了一拍,輸出時打了一拍。綜合后結果如下:

Number of Slice Registers: 2

Number of Slice LUTs: 19

Number of DSP48E1s: 11

關鍵路徑中數據路徑延時報告如圖2所示,數據路徑延時包括乘法器延時Tdspcko PCOUT AREG MULT (3.001ns)+ 10個級聯加法器延時Tdspdo PCIN PCOUT(1.219),數據路徑延時總共15.017ns,因此fmax最大不過66.273MHz。可以發現綜合器自動將乘法器和加法器在 DSP48E1中實現。

圖2

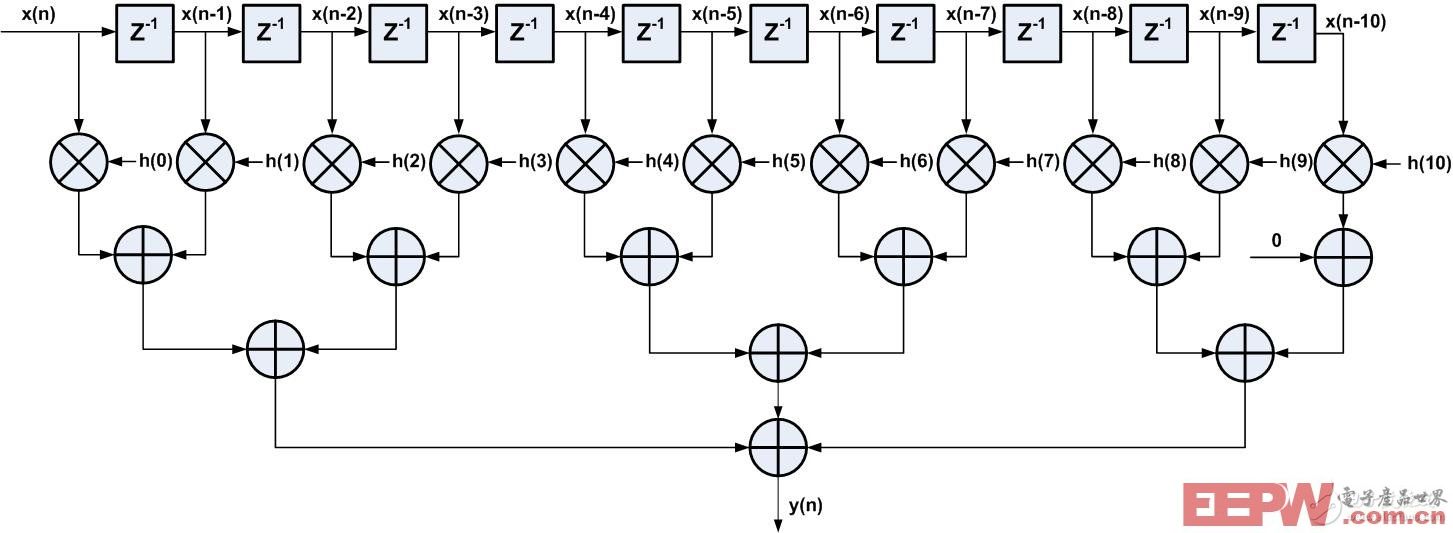

加法樹實現:

直接型FIR濾波器的一般實現方法關鍵路徑中有較多級的加法器,所有加法器延時累加后導致關鍵路徑延時較大,對整個FIR濾波器的性能造成了很大影響。為了解決加法器延時累加的問題,可采用加法樹結構,如圖3所示為采用了加法數的直接型FIR濾波器結構,這種層次化的樹型結構,使加法器邏輯由級聯結構轉化成并行結構,這樣整個路徑的延時減小。

圖3

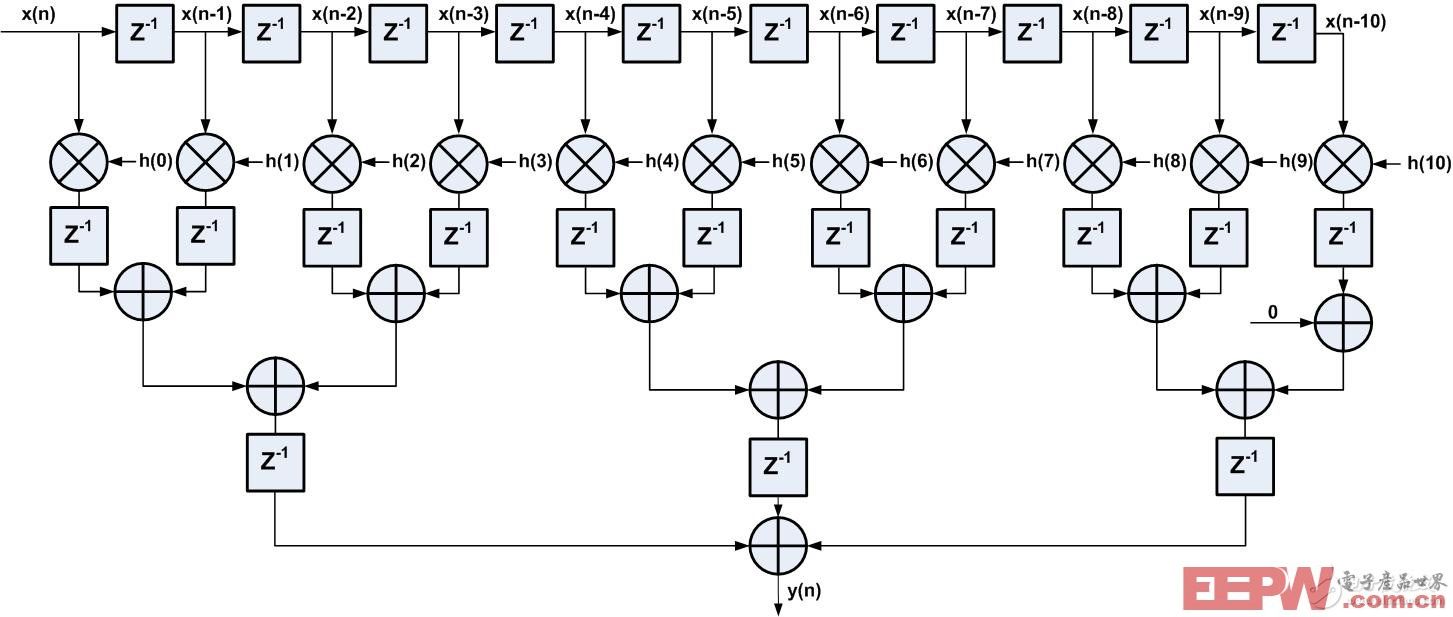

流水線實現:

雖然直接型FIR濾波器采用加法樹結構后優化了關鍵路徑,但是時序還是不夠理想,因為關鍵路徑上至少有一個乘法器和一個加法器的延時,如果想竟可能的優化時序,可以分隔乘法器和加法器邏輯,中間加一級寄存器,即采用流水線實現。

那如何有效地分割邏輯呢?可以在圖3中加法樹結構的基礎上分割,在原先的關鍵路徑上,乘法器延時3.001ns,加法器延時1.219ns,因此可以將邏輯分割成如下**:

第1級:乘法器

第2級:2級加法器

第3級:3個數累加即2級加法器

如圖4所示為流水線實現的FIR濾波器,邏輯分割后的關鍵路徑是乘法器那一級,理論分析得到的延時只有3.001ns,如果時鐘約束到250MHz可滿足時序要求。

圖4

實際得到綜合結果如下:

Number of Slice Registers: 105

Number of Slice LUTs: 124

Number of DSP48E1s: 11

Minimum period: 3.037ns{1} (Maximum frequency: 329.272MHz)

fmax能達到329.272MHz,延時基本與預期的差不多,FIR濾波器能達到這樣的性能基本能滿足大多數應用了。

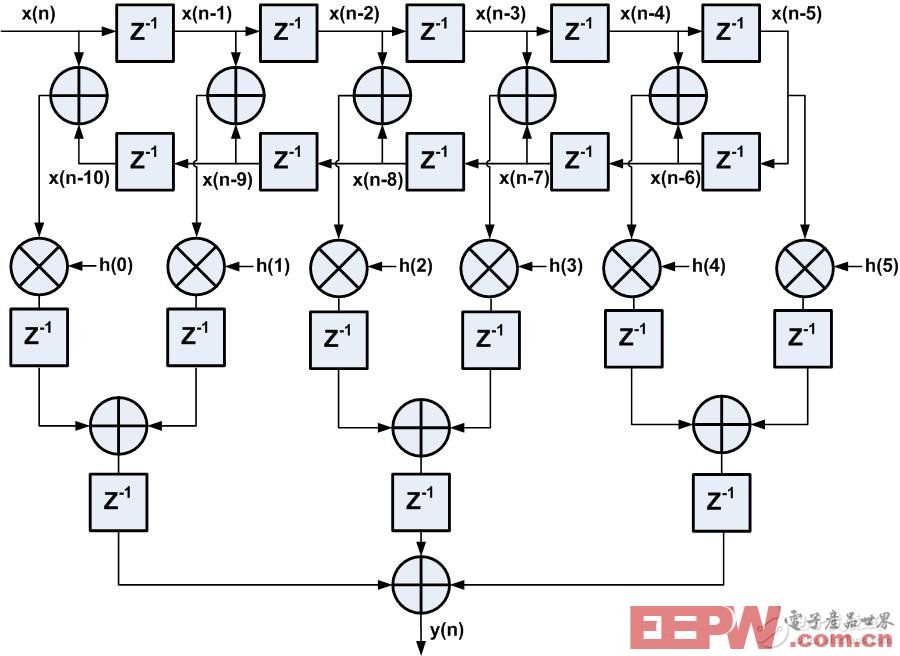

線性相位FIR濾波器:

FIR濾波器有一特征:線性相位,直接表現在抽頭系數上,抽頭系數為偶對稱或者奇對稱,在這節實例中,系數是偶對稱的,即 h(0)=h(10),h(1)=h(9),h(2)=h(8),h(3)=h(7),h(4)=h(6),直接型FIR結構優化后如圖5所示,輸入數據在與系數相乘之前,因系數對稱,可以先將相同系數對應的數據進行預加操作,然后再與系數相乘,如此做法的好處是是乘法器資源減少了近一半,此例中DSP資源由原先需要11個到現在只需6個。而且,在Xilinx FPGA中的DSP48E1資源專門為線性相位FIR濾波器應用提供了預加pre-adder結構,即預加和乘法都可以在1個DSP48E1中完成,這樣大大縮短了數據路徑的延時,有利于時序收斂。

圖5

實際得到綜合結果如下:

Number of Slice Registers: 184

Number of Slice LUTs: 173

Number of DSP48E1s: 6

Minimum period: 2.854ns{1} (Maximum frequency: 350.385MHz)

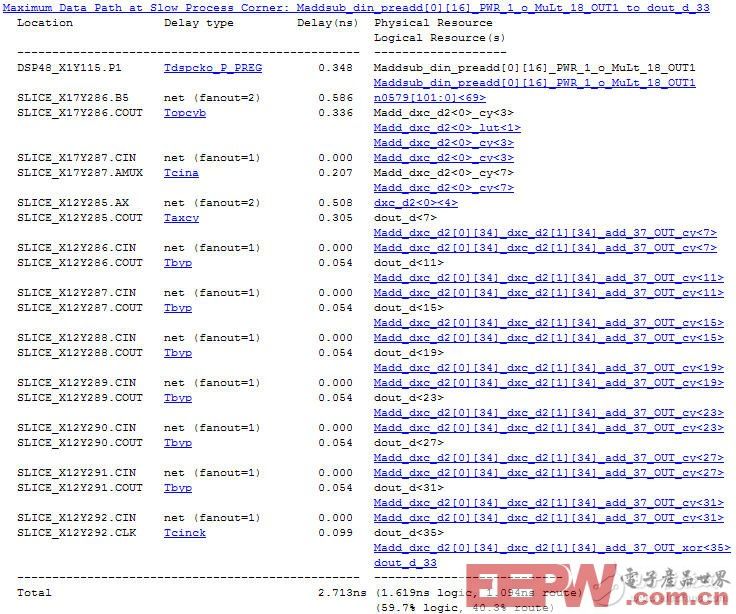

fmax能達到350.385MHz,由于采用了加法樹結構,避免了加法器級聯延時,并且分了3級流水線實現。關鍵路徑數據延時報告如圖6所示,路徑是從 DSP48E1輸出端到dout_d,但是光從代碼中看DSP48E1端到dout_d中間應該還有一級加法器的寄存,原來這個加法器采用了 DSP48E1中的累加器實現了。

圖6

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

高通濾波器相關文章:高通濾波器原理 數字濾波器相關文章:數字濾波器原理

評論