基于FPGA狀態機和片上總線的CompactPCI異步串口板設計方案

摘要:首先簡要介紹了CompactPCI異步串口板的通常設計方法,并且提出了這些方法的不足之處,重點闡述了基于FPGA狀態機和片上總線的新設計方案,以及該方案的技術優勢,隨后公布了基于該方案的異步串口板達到的性能指標。通過比較有關應答延遲的試驗數據,提出了基于FPGA狀態機和基于DSP處理器的異步串口板卡存在明顯的處理速度差異問題,并基于兩種設計方案,解釋了形成差異的原因。最后提出了FPGA狀態機對外部總線存儲器或端口的訪問管理性能大幅超越了任何一款DSP處理器的觀點,并對同行提出了類似研發項目的設計建議。

本文引用地址:http://www.104case.com/article/248894.htm引言

CompactPCI異步串口板安裝在工業計算機CompactPCI擴展槽內,可實現工業計算機與外圍多路設備串口之間的異步串行通訊。異步串口板有多種設計方案,不同的設計方案決定了板卡具有不同的通訊性能和可靠性。根據任務要求,某重要設備的測試平臺必須達到36路通道、11種通訊協議、波特率4/19.2/38.4/57.6/115.2(kbps)、小于1ms的處理時間、通訊模式可配置和高可靠性的試驗要求,因此測試平臺內異步串口板的設計方案要面向上述試驗要求而制定。

1 背景技術

1.1 現有技術

目前CompactPCI異步串口板一般采用以下兩類方法實現。

1.1.1 使用嵌入式處理器作數據處理單元

采用獨立的嵌入式處理器作為數據處理單元,異步串口單元要么使用嵌入式處理器自身的2到3個異步串口,要么使用連接到FPGA片內總線的通用異步收發器或異步收發邏輯,從而建立起一主多從式總線結構。

1.1.2 使用FPGA芯片集成收發邏輯和處理邏輯

采用FPGA芯片集成了若干獨立的異步串口通路,每個通路均有一對處理邏輯和收發邏輯,其中收發邏輯實現了一路串行數據的接受、發送和并串轉換,處理邏輯實現了一路串行數據的讀取、處理和存儲。

2 設計方案

2.1 設計思路

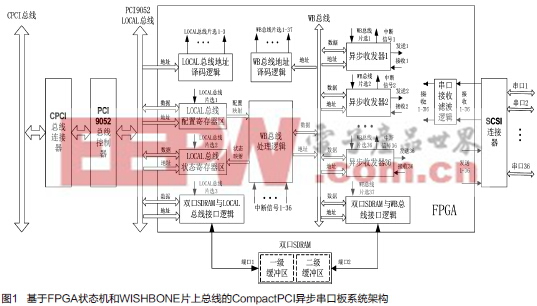

為便于性能比較,在采用第一類設計方案的總線式系統結構基礎上,分別用TMS320C6416 DSP處理器和FPGA狀態機作處理單元,實現了兩塊異步串口板(兩者系統結構、程序流程、通訊功能和軟硬件接口均相同)。每塊均在FPGA片上總線集成了36個UART軟核、1個雙口SDRAM接口邏輯、地址譯碼器、配置狀態寄存器區,以及串口接收濾波邏輯等,兩者不同之處在于FPGA狀態機作處理單元的串口板在FPGA上實現了一個完整的片上系統。下文重點介紹了后者的實現方法、性能指標,并對兩者的處理速度進行了比較和分析。

2.2 實現方法

2.2.1 板卡設計

基于FPGA狀態機和WISHBONE片上總線(圖中簡稱為WB總線)的36通路CompactPCI異步串口板系統架構如圖1所示。

fpga相關文章:fpga是什么

評論