淺談PCB中防止共阻抗干擾的地線設計

電子電路中,共阻抗干擾對電路的正常工作帶來很大影響。在PCB電路設計中,尤其在高頻電路的PCB設計中,必須防止地線的共阻抗所帶來的影響。通過對共阻抗干擾形式的分析,詳細介紹一點接地在電子電路中,特別是在高頻電路中對共阻抗干擾的抑制作用,以及采用一點接地防止共阻抗應注意的問題。

本文引用地址:http://www.104case.com/article/247930.htm0前言

在電子電路中,多數元器件都要通過地線形成回路,線設計合理與否,直接影響電路的工作。盡可能地降低由于地線設計不和理產生對信號傳輸的干擾。

在電路圖中,接地常用符號

1地線對電路產生干擾的形式

1. 1全電流共阻抗干擾

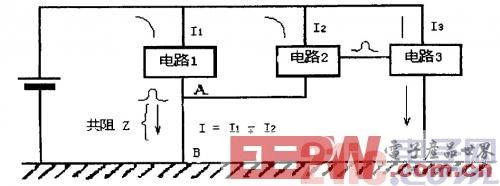

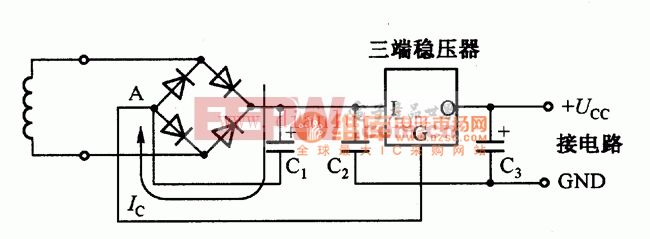

如圖1中,電路1和電路2通過公用地線AB與電源形成回路。線段AB可等效為一個電阻和電感的串聯回路,因而形成共阻抗效應。在工作時,電路1、2的電流變動,將引起A點電位變化,使電路1、2相互產生干擾。如電路2有輸出至電路3,干擾也將竄入電路3中,因此形成全電流共阻抗干擾。

例如有一段長為10cm,寬為1. 5cm的印制導線,其銅箔厚度為50微米,導線電阻為:

圖1地線共阻抗干擾

1. 2局部電流共阻抗干擾

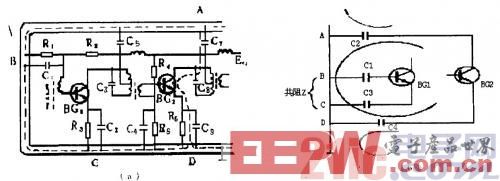

如圖2所示,當印制板采用環形地線,各接地元件按就近分散接地。這樣末級的交流信號一部分通過地線AD形成回路,在導線AD上產生交流壓降。

由于前級的晶體管發射極和基極與末級共用導線BC,在導線BC上產生共阻抗干擾。這種干擾是以局部電流的形式在公共地線上產生耦合,形成局部電流共阻抗干擾。

圖2另一種共阻抗干擾

全電流共阻抗干擾主要存在于級與級之間。局部電流共阻抗干擾則是指部分和個別元件與導線的接地點不良而對其他電路引起的干擾。

2防止共阻抗干擾的方法

各級內部接地。各級內部接地是防止局部電流共阻抗干擾的主要方法。即有效地防止了本級的交流信號通過各接地元件而逸出至本級以外的電路中去,或其他電路的交流信號,通過本級的各接地元件而檢拾進來。

無論對于低頻、中頻、還是高頻各級電路,防止局部電流的共阻抗干擾,唯一有效的方法是采用一點接地。

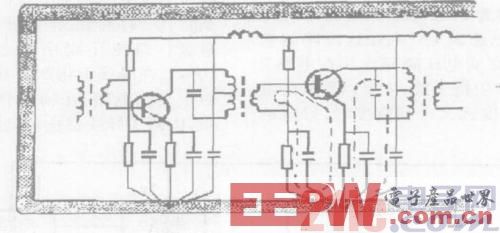

一點接地的形式如圖3所示。圖中將各級內部的接地元件,即本級電路的發射極基極和集電極的所有接地元件,均安排在一個接地點上與地線相接。

這樣,就能有效地防止交流信號通過接地元件的發散和接收,使接地純凈。

圖3一點接地

在實際電路中,各級的接地元件較多,不可能將這些元件同時穿入一個穿線孔內,而是將本級接地元件盡可能就近安排在公共地線的一段或一個區域內,如圖4a所示。有時遇到元件體積限制或排列上的原因,就近安排有困難時,可采用圖4b所示的接地形式,同樣可達到一點接地的效果。

圖4排版中的一點接地

電氣符號相關文章:電氣符號大全

評論