IC時鐘分配系統中的PLL

通過觀察利森方程式,我們便可發現VCO中相位噪聲的優化點:

本文引用地址:http://www.104case.com/article/246164.htm1. 調諧電路的負載Q值應最大化。可考慮串聯諧振電路內的大電感器或并聯諧振電路內的大電容器設計以實現該目標。負載Q值每上升10dB可改善20dB的相位噪聲。

2. 必須選用低等效噪聲電阻的變容二極管。同時推薦使用非線性程度低的變容二極管。

3. VCO調諧增益須保持在所需的最小值水平。

4. 必須選用可在低頻和低閃爍轉角頻率時產生低噪聲的有源設備。

5. 振蕩器的高輸入功率有益于降低噪聲。

當PLL用作時鐘合成器時,可削弱輸入源的噪聲并生成低噪聲輸出。若PLL的輸入源噪聲量很大,通常推薦使用低帶寬PLL對其進行濾波,但是降低PLL帶寬會導致VCO噪聲的相對貢獻上升。因此,通常應在PLL合成器內使用高品質的基準源,該基準源的噪聲性能應優于振蕩器的噪聲性能,方能對PLL的帶寬進行優化。

相位檢測器和充電泵噪聲:

相位檢測器和充電泵是PLL內與載波頻率接近的相位噪聲源。對比而言,VCO的主要噪聲貢獻則在載波器的遠端區間內,主要為超過環路濾波器截止頻率的部分。由于閉合環路中的PLL具有低通濾波器的功能,故相位檢測器、充電泵或基準噪聲源內超過環路濾波器截止頻率的噪聲通常均會被過濾。由于相位檢測器和充電泵的集成功能是檢測出基準信號和VCO輸出端反饋信號間的差異,并隨后生成誤差信號,故輸入信號相位的隨機變化會導致相位檢測器生成錯誤的輸出結果,該結果經濾波器傳輸后,會對VCO進行錯誤調諧,使人誤認為噪聲產生于PLL的輸出端。確保噪聲與基準值間盡可能產生最小偏離并同時最大化充電泵的增益,這樣可以降低相位噪聲。

分頻器噪聲:

PLL中的分頻器噪聲直接出現于相位檢測器的輸入端,且與輸入終端噪聲具有相同的傳遞函數;因此,該噪聲在環路濾波器截止頻率以下的近載波區間內同樣會對總體相位噪聲有貢獻。數字分頻器的多余噪聲可調節為其輸出端的加性噪聲源。

電源噪聲:

必須確保電源噪聲最小化,以降低PLL內的相位噪聲。電源噪聲的產生根源十分多樣,如調節器設計不合理、PCB噪聲耦合、電源內的噪聲未經適當濾波等。該噪聲可加大PLL模塊內的總體噪聲。

結論:

我們在本部分不僅了解了相位噪聲是PLL的關鍵參數之一,還分析了如何通過PLL級和系統級的悉心設計,采用優良的濾波電路、低噪聲源,以及最小化系統內所有其它可能的噪聲源等方法,從而最大限度地降低相位噪聲。

光耦相關文章:光耦原理

電容器相關文章:電容器原理

萬用表相關文章:萬用表怎么用

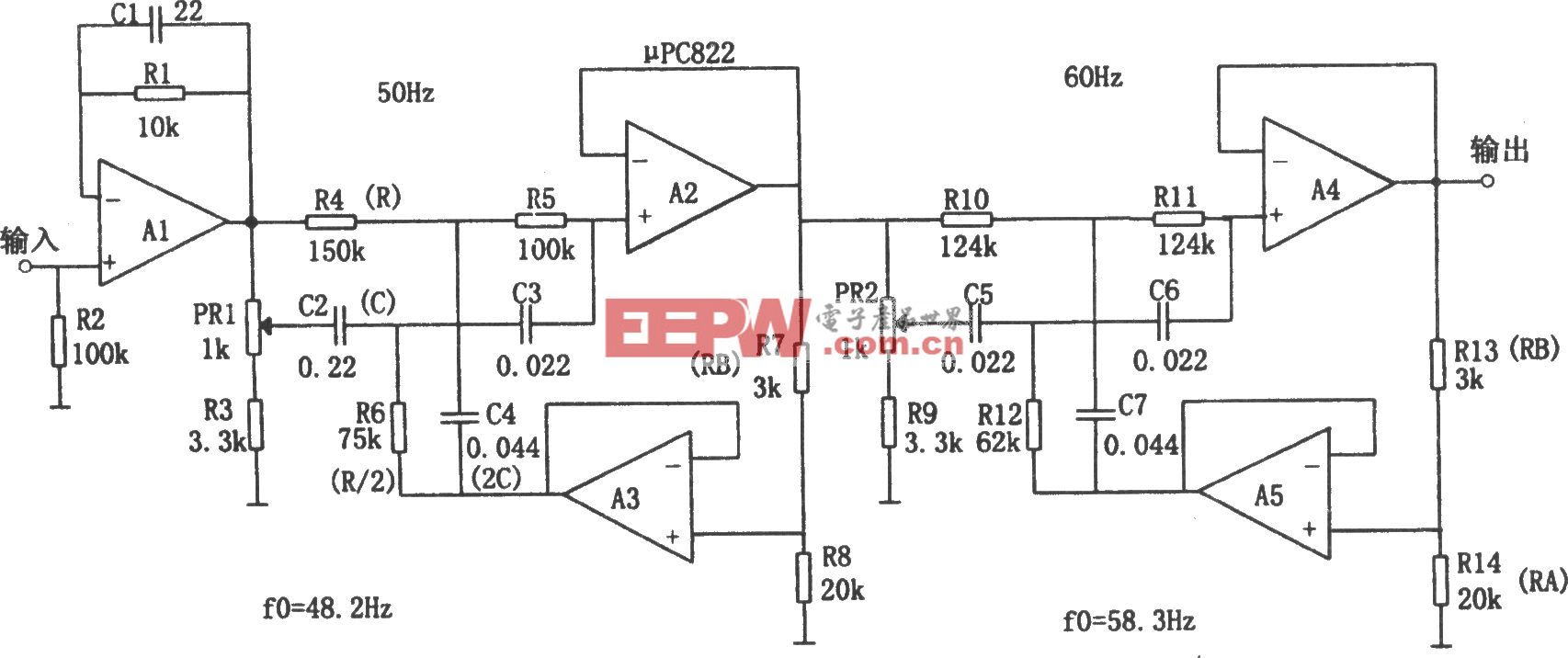

低通濾波器相關文章:低通濾波器原理

分頻器相關文章:分頻器原理 鎖相環相關文章:鎖相環原理

評論