IC時鐘分配系統中的PLL

閃爍噪聲:

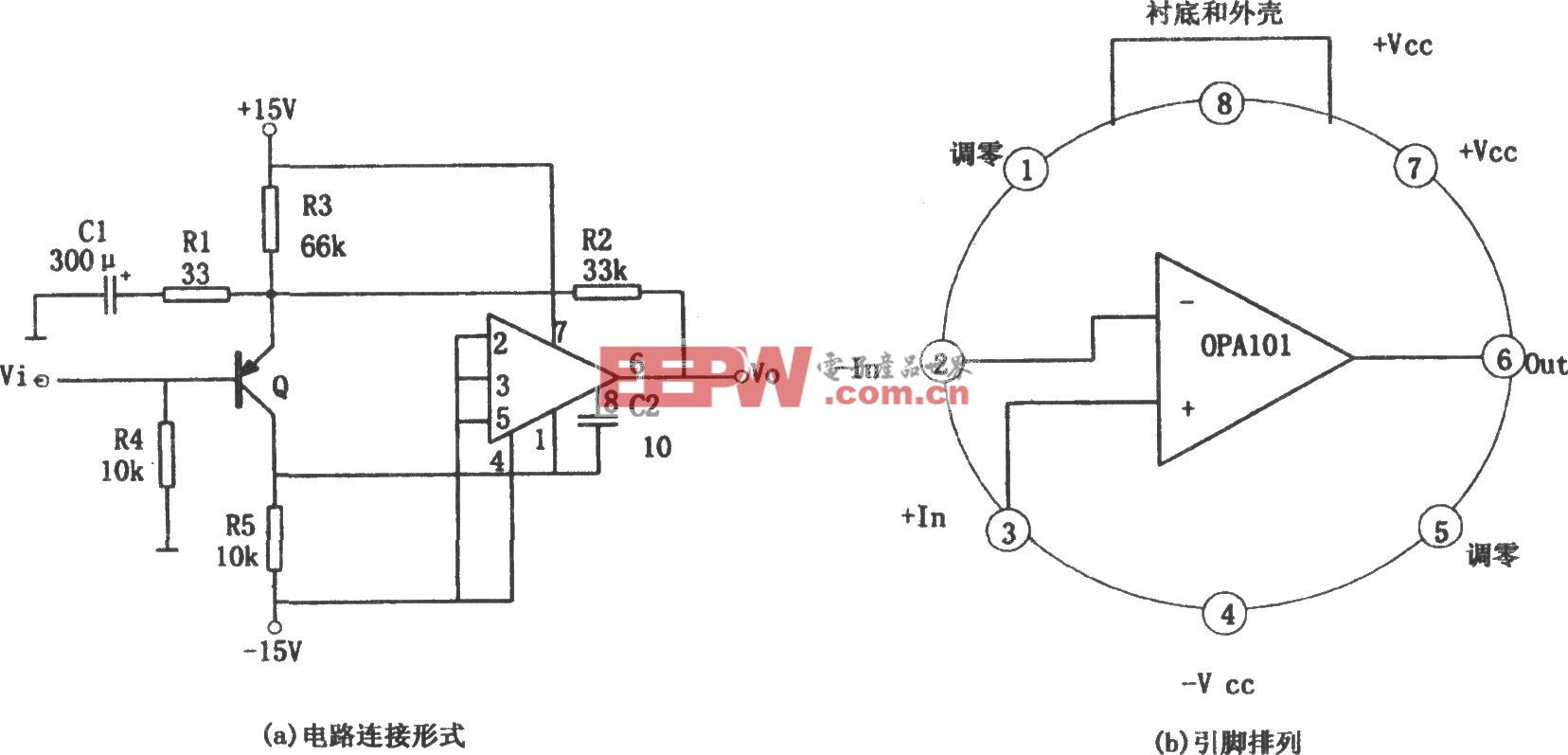

本文引用地址:http://www.104case.com/article/246164.htm閃爍噪聲用1/f表示,該噪聲在偏移角頻率fc處攔截熱噪聲底限,其頻譜與1/f相關。所有有源設備以及碳質電阻器等部分無源組件中均可發現該噪聲。閃爍噪聲的特點是,其大小與所觀察到的信號頻率成反比。閃爍噪聲是通過其頻率依賴性得到識別的,但其成因尚未明確。頻率小于100Hz時,閃爍噪聲將變得突出。使用繞線或金屬薄膜電阻器替代更加常見的碳質電阻器,便可大幅降低閃爍噪聲。

白噪聲:

噪聲的功率譜表明了任何給定頻率下噪聲功率的集中度。許多噪聲源均為“白色”,即其功率譜具有平坦性,即便在極高頻率時也是如此。換而言之,白色噪聲為常量值,與頻率無關。恒定帶寬的信號功率不會隨頻率變化而變化。繪制其與頻率關系圖便可發現,白色噪聲為圖5中水平線所示的恒定值。

PLL內的相位噪聲

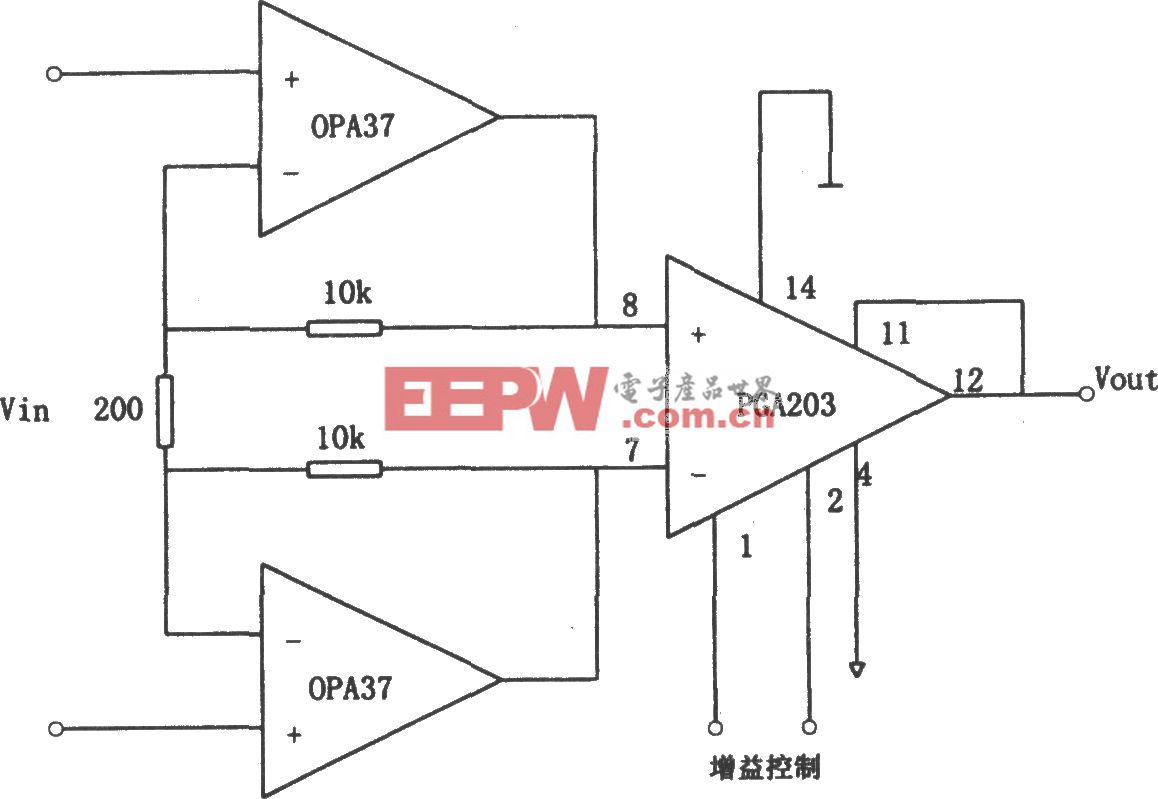

PLL屬于振蕩器類別之一,而在任何振蕩器設計中,頻率穩定性至關重要。高性能時鐘分配系統中,由于相位噪聲直接影響系統整體性能,故成為關鍵的考慮因素。其噪聲既可由各獨立模塊固有噪聲源產生,也可因電源噪聲及襯底噪聲等外部噪聲源與各模塊耦合后而產生。事實上,PLL內所有模塊均會或多或少地產生輸出相位噪聲。

研究總體相位噪聲的模塊前,讓我們再次回顧一下PLL的方框圖,如圖7所示。

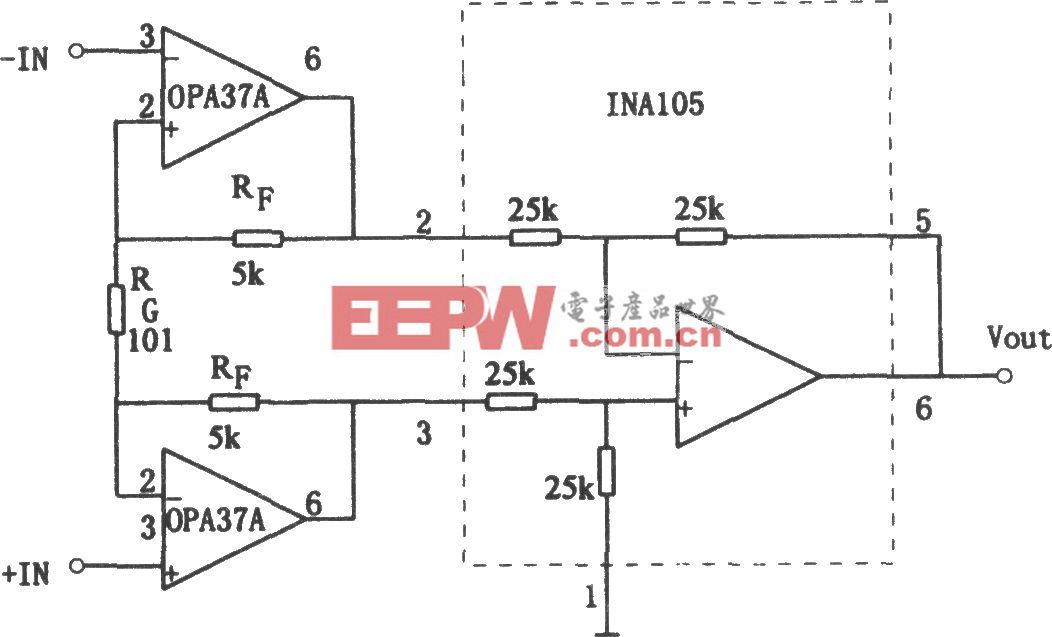

基準和VCO噪聲:

PLL有兩大噪聲源,即對PLL整體相位噪聲產生影響的基準振蕩器和VCO(電壓控制振蕩器)。基準噪聲源包括時序源噪聲、PCB噪聲耦合噪聲及電源噪聲,VCO噪聲源則包括環路濾波器組件、VCO放大器噪聲和電源噪聲。

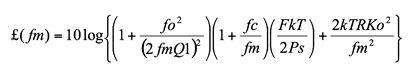

理想的VCO不會產生相位噪聲,且從頻域角度觀察時呈單一譜線,但現實情況并非如此,因為VCO的輸出抖動會產生擴頻,進而生成相位噪聲。可通過利森(Leeson)方程式充分理解VCO噪聲,同時還可通過對該方程式的研究,找到降低VCO噪聲的方法。表示振蕩器相位噪聲頻譜的利森方程式如下:

式中:

£(fm) 為偏移時的功率比

fm為振蕩器所生成的總輸出功率中的1Hz頻帶(單位:dBc/Hz)

fo為載波頻率

fm為偏移頻率

fc閃爍轉角頻率

Q1為諧振器的負載Q值(負載Q值指包括外部組件影響在內的品質因數)

F為噪聲因數

kT為室溫條件下的波爾茲曼常數

Ps為振蕩器輸入端的平均功率

R為調諧二極管的等效噪聲電阻

Ko為振蕩器的電壓增益。

光耦相關文章:光耦原理

電容器相關文章:電容器原理

萬用表相關文章:萬用表怎么用

低通濾波器相關文章:低通濾波器原理

分頻器相關文章:分頻器原理 鎖相環相關文章:鎖相環原理

評論