基于Nios II軟核的多核處理器系統的設計與實現

重要的是,在系統中互斥核Mutex本身無法從物理上防止共享資源被處理器同時訪問,而提供此功能是我們所編寫的軟件程序。在獲得相關共享資源前,軟件總是詢問并獲得Mutex核。

本文引用地址:http://www.104case.com/article/245929.htm2.2 軟件設計

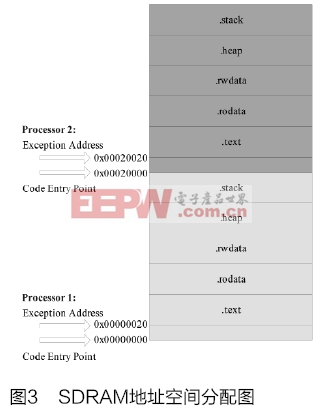

本設計中,兩個處理器的軟件程序都擁有自己獨有的一段存儲空間,這些存儲空間都位于同一個物理存儲設備SDRAM上,如圖3所示,第一個處理器使用SDRAM中0x0到0x1FFFF之間的地址空間,第二個處理器使用0x20000到0x2FFFF之間的地址空間,并且以異常地址作為邊界。

異常地址是程序加載的地址,決定著哪個處理器的軟件程序可以占據空間基地址運行。Nios II IDE負責鏈接處理器的軟件設計并映射到存儲器中,并為每個處理器提供其獨有的段空間來運行軟件設計。對于每個處理器來說,有五個主要的代碼段需要映射到存儲器的固定地址中:.text,存放實際執行的代碼;.rodata,存放實際執行代碼中所使用的常量;.rwdata,存放讀寫變量和指針;Heap,自動分配的空間;Stack,存放函數調用的參數和其他臨時的數據。

同時在雙處理器系統中,每個處理器都必須從自己的啟動存儲空間來啟動。啟動存儲器和程序存儲器一樣也能被分區,只需在存儲器上設置每個處理器的復位地址就可以。

3 系統軟硬件實現

SopcBuilder是Altera公司提供的一款圖形化系統設計實現工具,內嵌于Quartus II軟件中。利用SopcBuilder實現的雙核系統如圖4所示,包括了兩個Nios II軟核處理器以及其他內外設,連接關系表現了系統組件如何通過Avalon總線構成一個可以工作的系統。系統配置對每個系統組件分配了基地址,以實現Avalon總線對組件的訪問。

對于利用SopcBuilder生成的雙核系統,通過JTAG接口下載配置到Altera的FPGA開發板上,然后在Nios II IDE中調用HAL API函數開發C 語言應用程序就可以在FPGA開發板上運行,以此來驗證所設計的多核系統是否能夠正確運行。本文利用Altera公司提供的例程hello_world_multi,再將其修改后,各個處理器通過交替獲得Mutex的所有權,執行相同的程序,并將處理數據存儲在片上共享存儲器上,最終通過CPU_1的JTAG_Uart打印到Nios II IDE終端。圖5為驗證程序的運行結果在Nios II IDE輸出窗口的打印,可以看出,兩個核都能通過Mutex獲得外設的控制權,表明系統配置成功且能正確運行。

結語

本文根據SOPC技術利用Quartus的SopcBuilder構建硬件平臺,利用Nios II IDE運行軟件程序,實驗結果表明:軟硬件設計正確,系統能正常運行。同時,本設計為雙核以上的多核系統的設計提供了理論基礎。

存儲器相關文章:存儲器原理

評論