基于DSP/FPGA的超高速跳頻系統基帶設計

最上方信號是發射端跳頻序列的波形;中間信號是接收端跳頻序列的波形;最下方是幀同步信號。當識別到巴克碼時,幀同步信號出現一負脈沖,完成接收端調頻序列發生器反饋系數和初始相位的加載。從圖9中可知:(1)接收端跳頻序列與發射端跳頻序列變化規律一致,跳頻圖案同步成功;(2)最小碼距滿足要求,通過對偶頻帶法得到寬間隔跳頻序列成功。

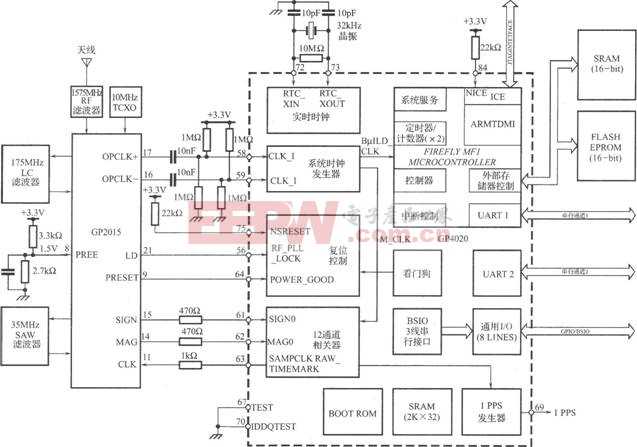

系統以TI公司DSP為中心控制單元,Altera公司的FPGA為硬件邏輯平臺,AD公司的DDS為頻率合成器,采用2FSK調制解調方式,超前滯后支路的位同步方式,TOD跳頻圖案同步方式,以m序列作為跳頻序列,輔助對偶跳頻間隔控制手段,實現了高速、寬間隔跳頻通信系統。系統達到40kbps的跳頻速度,1 024個跳頻頻道,108M~189.84MHz的跳頻帶寬,400kHz的最小跳頻間隔,小于0.5s的入網時間以及小于30s的同步最大時差。

本高速跳頻通信系統與同類系統相比最大的優勢體現在它40kbps的超高速跳頻速率和近百兆的跳頻帶寬上。通過與國內外類似系統進行比較,40kbps的跳頻速率處于技術領先位置。各關鍵模塊性能優良,接口一致且工作穩定,可以靈活組合成多種數字通信系統的基帶部分。相信本文對今后數字通信系統基帶部分的研究和實現具有很強的借鑒意義。

參考文獻

1 梅文華. 跳頻通信.北京:國防工業出版社,2005

2 夏宇聞.Verilog數字系統設計教程.北京:北京航空航天大學出版社,2003(第1版)

3 Uwe Meyer-Baese著,劉 凌,胡永生譯.數字信號處理的FPGA實現.北京:清華大學出版社,2003(第1版)

4 梅文華,張志剛.一類新的寬間隔跳頻序列族的構造[J].電波科學學報,2002;17(1):16~20

5 張申如,梅文華,王庭昌.計數式TOD跳頻碼發生器算法的構造.電子與信息學報,2002;24(8):1096~1101

6 TI.TMS320C5000 Assembly Language Tools User′s Guide[M].2002

7 TI.TMS320C5000 Chip Support Library API Reference Guide[M].2002

8 Altera. Cyclone Datasheet[M].2004

評論