基于DSP/FPGA的超高速跳頻系統基帶設計

為了適應復雜的數字接口,在FPGA中設計了DDS Controller邏輯,完成了對所有時序和數據格式的轉換。DSP僅通過讀寫DDS Controller中的幾個寄存器就可以實現對DDS的所有操作。DDS的輸出端采用了互補電流輸出,經過變壓器耦合并通過低通濾波器后得到基頻信號。

3.2 調制解調FPGA邏輯設計

本系統采用了2FSK調制方式。2FSK調制實際上就是根據二進制碼流的極性輸出頻率f0(頻點0)或頻率f1(頻點1),跳頻通信系統根據跳頻圖案決定載波頻率,但歸根結底就是改變DDS的輸出信號頻率。

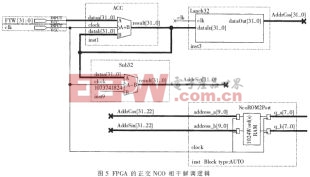

本設計采用了相干解調方式,圖5給出FPGA的正交NCO相干解調邏輯圖。

圖5中ACC為32bit相位累加器,Sub32提供π/2的相位平移得到Q支路的波表地址,Lanch32的作用是使相位累加器的輸出結果延時一個時鐘周期,保持I、Q支路嚴格同步,因為Sub32的運算會使Q支路延時一個時鐘周期。雙口ROM存儲余弦表,同時產生I支路和Q支路的波形。

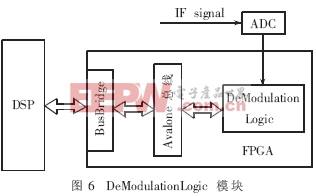

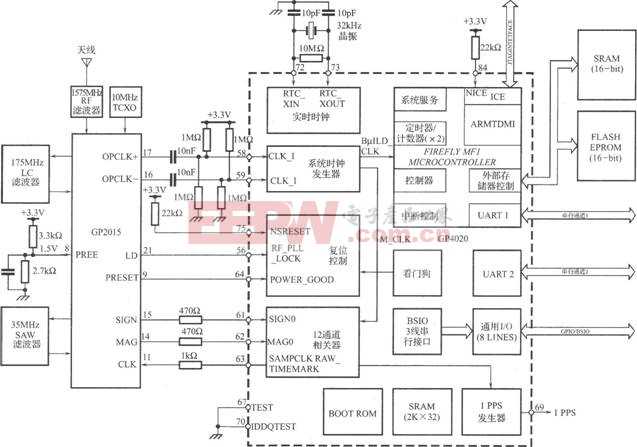

正交NCO、數字混頻器、低通濾波和采樣調整模塊共同構成了解調單元DeModulationLogic。DeModulationLogic在FPGA系統中的位置如圖6所示。

3.3 跳頻序列的DSP控制設計

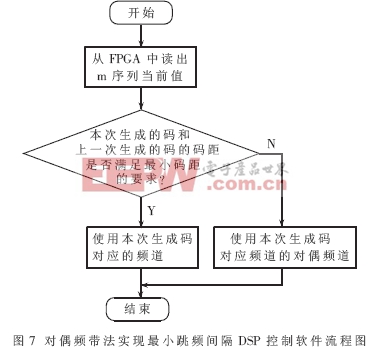

跳頻序列是決定跳頻通信系統跳頻圖案的偽隨機序列。對跳頻序列的要求是循環周期長、最小碼距大、隨機性強等。本設計采用了理論研究最完備、易于產生的m序列作為跳頻序列,在DSP中通過軟件實現對偶頻帶法對最小跳頻間隔的控制,DSP判斷相鄰兩次生成的m序列的碼距是否符合要求。若不符合最小碼距的要求,則跳到此次生成碼的對偶頻道上去。如圖7所示。

3.4 同步設計

同步是跳頻通信系統的核心技術。跳頻通信系統的同步包括載波同步、位同步和幀同步(跳頻圖案同步)。

由于本設計采用2FSK調制解調方式,所以僅需要接收端提供一個與所接收到的載波信號同頻的本地載波信號即可,因而可以不進行載波跟蹤,直接通過設置頻率合成器的頻率控制字實現收發同頻即可實現載波同步。

位同步是以解調電路為基礎的。由于碼速率較高,位同步運算大都在FPGA中通過硬件完成。

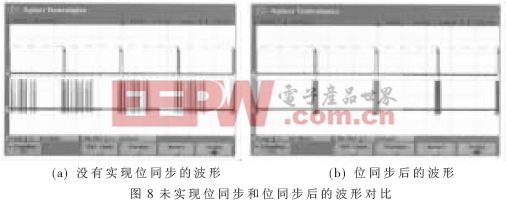

圖8(a)是沒有同步時的示波器波形圖,圖8(b)是同步后的示波器波形圖。通道一(上方)是發送端的發送脈沖,通道二(下方)是接收端的位同步脈沖。位同步以后,接收端的位同步脈沖和發射端的發射脈沖完全對齊,波動范圍不超過1μs, 最大偏移不超過碼元寬度的4%。圖中,時間:5μs/格;電壓2V/格(上);電壓2V/格(下)。

跳頻圖案同步是跳頻通信系統中特有的同步概念,它是指接收方的跳頻圖案與發射方跳頻圖案保持一致的過程或狀態。在跳頻通信系統中,幀同步和跳頻圖案同步概念相似,有時候不加區分, 本設計選用13位巴克碼{1,1,1,1,1,-1,-1,1,1,-1,1,-1,1}作為幀同步信號。圖9是FPGA中信號跳頻圖案同步示意圖。

相關推薦

-

liujt_ic | 2003-05-15

-

-

-

-

herbertwj | 2004-08-15

-

-

-

-

-

xiaohua | 2002-09-24

-

-

fancy_wind | 2004-10-29

-

liujt_ic | 2003-03-21

-

評論