基于FPGA的數字下變頻電路的設計與實現

低通濾波器的實現:

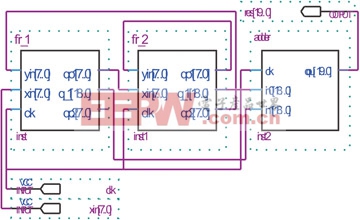

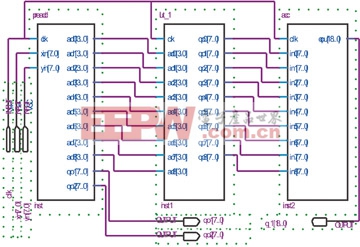

數字下變頻器的最后一個模塊是低通FIR濾波器,主要用來對信號進行整形濾波,消除信號中存在的噪聲。本設計采用并行結構的FIR濾波器,由2個8階濾波器級聯實現16階的濾波器,由預相加模塊、查找表模塊和移位相加模塊組成,結構圖如圖3、4所示。

圖3 16階FIR濾波器的級聯結構圖

圖4 FIR濾波器子模塊結構圖

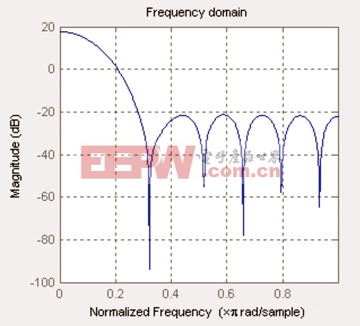

圖5 16階FIR濾波器響應曲線圖

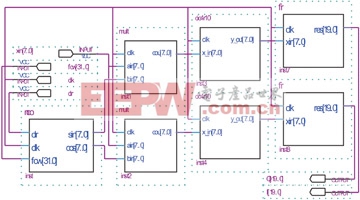

圖6 DDC實現的結構圖

這種結構的濾波器結構簡單、易于實現,很容易擴展成高階濾波器。首先通過MATLAB中的Fir DesignTool工具得到濾波器的系數圖表(表1)。利用線性FIR濾波器抽頭系數的對稱性,通過加法器將對稱的系數進行預相加,從而降低硬件規模。根據分布式算法原理,通過將抽頭系數的所有可能組合固化在ROM中,利用查找表來代替乘法器。利用預相加模塊產生的地址來查找ROM表,并將相應的數值進行移位相加,從而得出正確的結果。

表1 16階FIR濾波器系數

DDC系統的實現

利用上述的各個模塊,可得到DDC系統的實現結構圖如圖6所示。

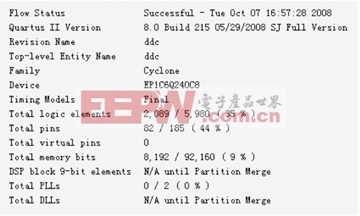

整個系統在Cyclone系列芯片EP1C6Q240C8上實現,其FPGA綜合結果圖7所示。

圖7 DDC系統的Quartus綜合結果

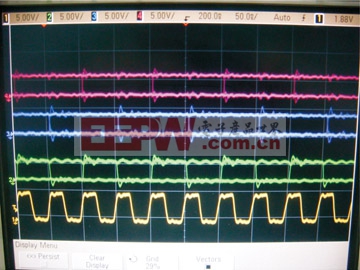

圖8 系統時序測試結果

時序測試圖(圖8)中,黃色為系統時鐘波形,綠色為NCO產生的正弦波時序波形,藍色為抽取濾波器輸出的時序波形,粉紅色為FIR濾波器輸出時序波形。從示波器顯示的時序圖可以看出抽取濾波器輸出波形的延時最大,大約為14ns左右,這和軟件仿真的結果比較吻合,仿真中抽取濾波器輸出的延時為16.47ns。故抽取濾波器是制約系統時鐘速率提高的關鍵因素。

結語

評論