基于FPGA的數字下變頻電路的設計與實現

引言

數字化中頻(DIF)頻譜分析儀在高中頻實現數字化處理,具有分析帶寬大、RBW小、測量時長短,可對復雜信號實施時—頻分析的功能,因而得到越來越廣泛的應用。但由于現有的數字信號處理器(DSP)處理速度有限,往往難以對高速率A/D采樣得到的數字信號直接進行實時處理。為了解決這一矛盾,需要采用數字下變頻(DDC)技術,將采樣得到的高速率信號變成低速率基帶信號,以便進一步的分析處理。用現場可編程陣列(FPGA)來設計數字下變頻器有許多好處:FPGA在硬件上具有很強的穩定性和極高的運算速度,在軟件上具有可編程的特點,可以根據不同的系統要求,采用不同的結構來完成相應的功能,具有很強的靈活性,便于進行系統功能擴展和性能升級。

數字下變頻的主要目的是經過數字混頻將A/D轉換輸出的中頻信號搬移至基帶,然后通過抽取,濾波完成信道提取的任務。因此,數字下變頻器由本地振蕩器(NCO)、混頻器、抽取濾波器和低通濾波器組成,如圖1所示。

圖1 數字下變頻原理圖

A/D變換后的信號分成兩個信號,一個信號乘以正弦序列(同相分量),下變頻至零中心頻率上,通過抽取濾波器、整形低通FIR濾波形成與原信號相位相同的信號;另一路信號乘以經過90度相移的正弦序列(正交分量),同樣是下變頻至零中心頻率上,再通過相同的抽取濾波器、整形低通FIR濾波器,形成與原信號正交的信號。這樣,DDC輸出的低速率、零中頻的正交的兩路信號送往DSP等數字信號處理器進行后續的數字處理。

DDC的FPGA

以某中頻數字化接收機為例來說明如何實現基于FPGA的數字下變頻器。輸入信號為中頻26MHz,帶寬500KHz的調頻信號,該信號經過A/D變換之后送到DDC(A/D采樣精度為8位,采樣率20MHz),要求DDC將其變換為數字正交基帶信號,并實現10倍抽取,即輸出給基帶處理器的數據速率為2MSPS,最后再經過16階FIR濾波器進行信號整形。

NCO的實現

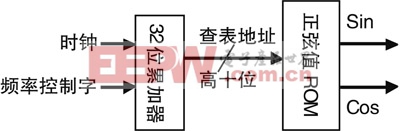

NCO采用直接數字合成(DDS)的方法實現,目前常見的技術有查表法和CORDIC計算法,本設計采用查表法來實現NCO,其原理圖如圖2所示。

圖2 NCO原理圖

32位累加器由一個32位的加法器和一個32位寄存器組成,在時鐘的作用下,加法器通過寄存器將輸出數據送入到加法器的一個輸入端,與32位的頻率控制字進行相加運算,得到一個有規律的相位累加結果。由于正弦值在一個周期內取有限個采樣值,大于2pi部分的正弦值只是這有限數值的重復出現,因此,當累加結果大于FFFFFFFFH是,不需產生進位,而是重新從00000000H開始累加。為了減小ROM的容量,根據相位截斷技術,取累加器輸出的高10位作為查表地址,但是這種實現方式,在降低成本的同時,也引入了雜散分量,影響了NCO的純度。正弦值ROM中存儲的是預先計算好的正弦波幅值,利用正弦波的對稱特性,只需存儲四分之一周期的幅值,再通過相應的轉換即可恢復出整個周期的幅值。同時,由于余弦波和正弦波相位差為pi/2,可以很容易的實現余弦信號。其關鍵部分的VHDL代碼如下:

process

begin

wait until clk=’1’;

if add(8)=’0’ then

address=add(7 downto 0);

else

address=”11111111”-add(7 downto 0);

end if;

if add(9)=’0’ then

qou(7)=’0’;

qou(6 downto 0)=q;

else

qou(7)=’1’;

qou(6 downto 0)= ”1111111”-q;

end if;

end process;

抽取濾波器的實現

CIC積分梳狀濾波器是實現高速抽取非常有效的單元。CIC濾波器的系統函數為:

![]()

式中D即為CIC濾波器梳狀部分的延遲,濾波器系數都為1。從上式可以看出CIC濾波器的實現非常簡單,只有加減運算,沒有乘法運算,FPGA實現時可達到很高的處理速率。但是,單級CIC濾波器的旁瓣電平只比主瓣低13.46dB,這就意味著阻帶衰減很差,一般是難以滿足實用要求的。為了降低旁瓣電平,可以采取多級CIC濾波器級聯的辦法解決。在CIC濾波器的實現過程中,需要給內部寄存器提供足夠的位寬,其計算公式為:

![]()

其中N為級數,M為延遲,R為抽取倍數。

本設計中,CIC濾波器需要完成10倍的抽取,采用4級級聯來實現,由于輸入、輸出數據均為8bit,故內部寄存器所需的最大位寬為,旁瓣容限可達到4×13.46=43.44dB。

CIC濾波器實現的關鍵是抽取器的分頻設計,其VHDL代碼如下:

signal count : integer range 0 to 9;

signal clk2 : std_logic;

if (count=9) then --抽取器分頻實現

clk2=’1’;

else

clk2=’0’;

end if;

comb : process --抽取器代碼

begin

wait until clk2=’1’;

i3d1=c0;

…………

c4=c3/2-c3d1;

end process comb;

評論