OPB總線仲裁器的RTL設計與FPGA實現

0 引言

隨著 SOC 設計技術的發展,為了使IP 核集成更快速、更方便,縮短進入市場的時間, 迫切需要一種標準的互聯方案。CoreCONnect 正是在這一背景下為SOC 設計的總線架構。按 照數據訪問速度它可分為三層總線,分別是處理器內部總線PLB(Processor Local Bus)、片上 外圍總線OPB(On-ChipPeripheral Bus)和設備控制總線DCR(Device Control RegiSTer)。 OPB 總線是為UART、GPIO 等慢數據率設備提供接口的總線。由于集成到總線中的功能模 塊越來越多,對于共享總線系統,片上仲裁是使得各個模塊有效運作的必要手段。目前關于 OPB 總線仲裁器這方面的研究報道較少,為了探尋在不同的系統負載和系統應用下選擇最 佳的OPB 總線仲裁方案,本文基于固定優先級和LRU 兩種算法,利用自頂向下的設計方法, 設計了OPB 總線的仲裁器,并對其綜合結果做了比較。

1 OPB 總線仲裁機制

OPB 總線支持32 位數據/地址位寬,讀和寫數據總線分開,支持重試模式,支持突發 (burst)傳輸模式,支持DMA,檢測總線超時功能,支持多個主設備的仲裁。OPB 總線的 系統結構分為三個部分:主設備(Master),從設備(Slave)和總線邏輯。信號命名有三種: Mn_打頭的,是master 的輸出;Sln_打頭的,是Slave 的輸出;OPB_打頭的,是總線邏輯 的輸入或輸出。OPB 總線允許有多個master,當這幾個master 同時發出請求要求使用總線時, 就必須對他們的請求進行仲裁,并確定他們使用總線的優先級,這就是仲裁器的作用。OPB 總線仲裁器的輸入輸出信號如圖1 所示。

SYSCLK 和RESET 為OPB 總線的系統時鐘和復位信號。Mn_REQUEST 為4 個master 的請求信號,OPB_MnGRANT 為仲裁器發出的授權信號,OPB_select 是master 收到授 權信號后發出的占用總線信號,OPB_ABUS 為地址總線,OPB_DBUS 為數據總線, OPB_XFERACK 為slave 數據傳輸完的響應,OPB_RNW 是讀寫使能信號,OPB_BUSLOCK 是master 鎖定對總線使用權的信號,ARB_DBUS 和ARB_DBUSEN 是仲裁器的數據總線和 使能信號,ARB_XFERACK 是仲裁器傳輸數據完成的響應信號。OPB_TOUTSUP 是slave 超時禁止的信號,OPB_TIMEOUT 是總線超時信號。

仲裁過程說明如下:

Master 首先發出Mn_REQUEST 信號申請占用總線,仲裁器根據總線占用情況和優先權 算法發出OPB_MnGRANT 信號,得到最高優先權的master 拉高Mn_SELECT 信號,其他 master 把這個信號置低,這4 個select 信號通過或邏輯形成OPB_SELECT 信號輸入給仲裁 器。

同時發送地址 Mn_ABUS,也是通過或邏輯轉變成OPB_ABUS 輸入給仲裁器。OPB 總 線有多個slave 設備,每個slave 都有自己的地址空間值,Master 發送的Mn_ABUS 正是包 含了他所要使用的slave 的地址值,slave 會對值進行比較,如果相等,master 就可以對slave 進行讀寫操作。

讀操作時,master 拉高OPB_RNW,仲裁器拉高ARB_DBUSEN,并通過ARB_DBUS 輸 出數據。寫操作時,master 拉低OPB_RNW,通過OPB_DBUS 輸入數據。當有效數據傳輸完 成后,仲裁器會拉高ARB_XFERACK 信號響應。Master 在收到響應后,會拉低Mn_SELECT 信號,結束此次總線事務。

2 OPB 總線仲裁器的設計

采用自頂向下的設計方法,將設計分成4 個模塊,分別為優先級邏輯模塊,仲裁模 塊,看門狗超時模塊和鎖定/停靠模塊。原理圖如圖2 所示。

圖2 仲裁器設計原理圖

1) 優先級邏輯模塊

這個模塊采用兩種不同的算法進行設計,分別是LRU(Least Recently Used)算法和固定 優先級算法[1]。

a) LRU 算法

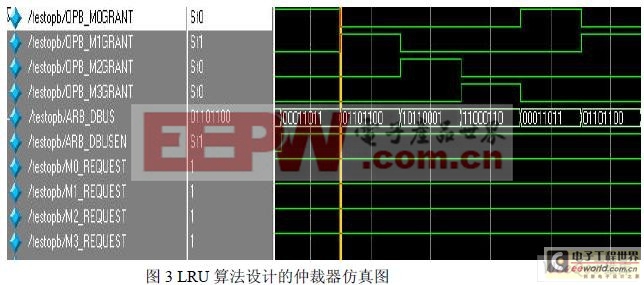

LRU 算法就是根據master 的編號循環得到優先級,保證每個設備都有機會獲得總線。我 們設計的是最多支持4 個master 的仲裁器,所以采用一個8 位的寄存器,用來存放4 個master 的二進制編號。每個周期都要更新這個寄存器值,將得到最高優先級的master 編號放到最 低優先級,其他3 個master 編號各進一級。用這種算法設計的仲裁器的仿真結果如圖3。

其中 ARB_DBUS 讀出來的數據正是寄存器中保存的master 編號,優先級從高位到低位 遞減。00,01,10,11 代表master 的編號0,1,2,3。當4 個master 同時發出請求時,第 一個時鐘周期將優先級授權給master0,第二個時鐘周期時,master0 的優先級降為最低,其 他三個優先級遞進,所以此時授權給master1。后面的周期依次循環,4 個master 將輪流獲 得授權。

b) 固定優先級算法

固定優先級算法將 4 個master 的優先級按順序固定下來,不會改變[2]。這種算法設計更 簡單,不需要每周期對master 的優先級更新。設計時優先級寄存器中的值只在總線執行寫 操作和復位時才會改變,平時固定不變。仿真結果見圖4。

ARB_DBUS 是寫入的4 個master 的優先級順序,master0 為最高,master3 最低。當4 個master 同時發出請求時,授權給master0;當master0 不發出請求,其他三個master 發出 請求時,則根據優先級順序,授權給master1;依此類推。

2)仲裁邏輯模塊

從優先級邏輯模塊得到的優先級寄存器信號,將被輸入到仲裁邏輯模塊。用以對4 個 master 的Mn_REQUEST 請求信號排序,然后優先級從高到低排序的master 中,第一個拉高 請求信號的master 將被授權占用總線。仲裁邏輯模塊輸出的授權信號是最原始的,這個信 號還要經過鎖定/停靠邏輯模塊處理才能得到最終的授權信號(OPB_MnGRANT)。

3) 看門狗超時邏輯模塊

看門狗邏輯用來監控OPB 的控制信號,當master 在16 個時鐘中期內沒有能夠收到slave的響應信號( OPB_XFERACK ) 和超時禁止信號( OPB_TOUTSUP ), 將會拉高 OPB_TIMEOUT 超時信號[3]。這部分的設計采用一個4 位計數器對時鐘進行記數。

4) 鎖定/停靠邏輯模塊

優先級鎖定是得到最高優先級的master 同時拉高OPB_BUSLOCK 信號,這樣在這個信 號被置低之前,這個master 將始終得到總線的占用權,仲裁邏輯將不啟用。此時不管master 是否發送請求,都不會對仲裁產生影響。優先級的鎖定是通過將仲裁邏輯得到的原始優先級 信號和OPB_BUSLOCK 信號相與后產生的。優先級停靠是當沒有新的master 發出請求信號 時,總線繼續授權給當前占用總線的master。這里設計了一個四位寄存器用來追蹤最近占用 總線的master 編號。

最后,通過altera 公司的CycloneII FPGA 對兩種設計進行綜合[4],并對綜合結果進行比 較。并采用cadence 公司的conformal 進行RTL 代碼和網表之間的形式驗證。表1 為綜合 和形式驗證結果。

得出的結論是:固定優先級算法設計簡單,占用資源少,可以達到較高的應用頻率。但 這種算法使優先級高的設備占著總線不放,當總線事務繁忙時,優先級低的設備將申請不到 總線,所以只適用于總線使用率低,負載低的應用。而LRU 算法雖然更占資源,頻率也低 點,但這種算法授權更加公平,使所有設備都有機會申請到總線,適用于總線使用率高,負 載高的應用。

3 結束語

本文通過對 OPB 總線仲裁器兩種算法的研究,比較了兩種算法的性能優劣并得出結論, 固定優先級算法設計簡單,占用資源少,可以達到較高的應用頻率,能夠保證主要處理器的 運行速度,但缺乏公平性;LRU 算法更占資源,頻率較低,但具有公平性,適用于總線使 用率高,負載高的應用。對不同的總線負載和使用率情況下選擇最佳的OPB 總線仲裁方案 提供了依據,對高效的系統設計和嵌入式應用有重要的參考價值和指導意義。

評論