基于FPGA的動態局部可重構實現方法

1 Xilinx的EAPR局部重構流程

EAPR(early access partial reconfiguration)與基于模塊(module based)流程相比,有以下的主要區別:

I 移除了Virtex-II器件局部可重配置(PR)中對于局部可重配置區域必須是整列的要求,EAPR設計流程中,允許PR區域為任意矩形區域;

II 總線宏使用基于SLICE來實現,而不是基于TBUF的總線宏,這就使得允許使用的總線宏的密度更密;

III EAPR流程中允許基于模塊設計中的全局信號直接穿越局部可重配置區域,而不必使用總線宏。這一改進顯著地改進了時序性能,并簡化了PR設計的編譯進程;

IV 移除了需要在基于模塊的設計中對AREA_GROUP RANG進行面積約束的限制,這樣就給PR設計的布局布線提供了更大的靈活性;

V 現在的EAPR設計流程及工具支持Virtex 4和Virtex5 器件。

2 建立局部重構

局部重構的設計和實現流程可分為以下步驟:

①設計輸入與綜合:按照Xilin的EAPR設計流程的要求輸入與綜合HDL代碼,包括頂層模塊和子模塊設計,頂層模塊設計完成頂層模塊的設計輸入與綜合;子模塊設計可進行子模塊的設計輸入和綜合。

②初始預算(initial budgeting):指構思平面布局,完成對頂層模塊和每個子模塊的時序約束,頂層約束包括對整個設計的全局區域約束、對每個子模塊的規模和區域的約束、對每個模塊的輸入/輸出約束和對整個設計的時序約束等內容;

③子模塊的激活實現(active module implementation):對每個子模塊進行激活實現,對每個子模塊內部的邏輯進行單獨約束;

④合并實現(final assembly):將頂層設計與已激活實現的模塊合并,形成一個完整的設計;

⑤驗證:包括靜態時序分析和功能仿真;

⑥檢查設計:用FPGA editor工具檢查布線跨越模塊的邊界;

⑦創建初始上電的配置文件;

⑧創建重構模塊的配置文件;

⑨加載初始上電的配置文件;

⑩進行局部重估操作;

3 動態局部重構系統結構

在局部重構的建立完成后,必須依托嵌入式開發套件(EDK,Embedded Development Kit)來進一步完成設計,使系統具備自重構能力,也就是能實現真正意義上的動態局部重構。

3.1 將處理器系統作為內部模塊的動態局部重構系統實現方案

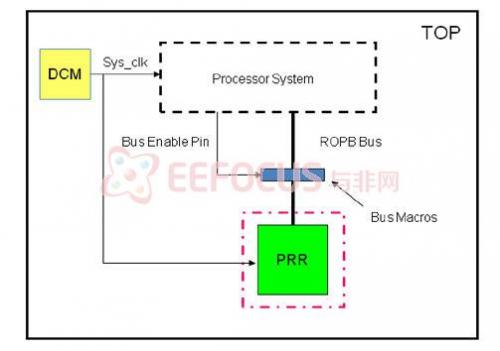

該實現方案借助嵌入式開發套件EDK建立一個處理器系統,同時借助Xilinx ISE工具建立一個頂層模塊,該頂層模塊包含了作為子模塊的處理器系統和同樣作為子模塊的局部重構模塊。完整的系統如下圖所示:

圖1 完整的系統視圖

其中,PRR(Partial Reconfiguration Region)是局部可重構模塊,它與處理器模塊通過內部ROPB Bus連接,同時作為可重構模塊與靜態模塊的連接還必須有總線宏Bus Macros。

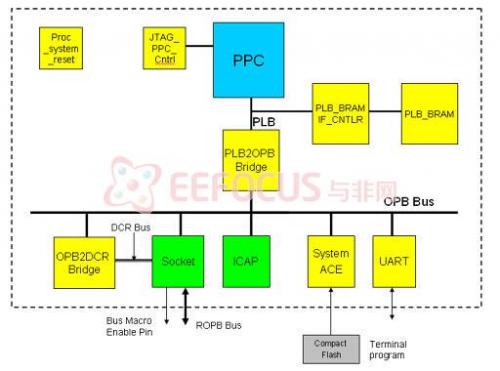

處理器系統內部結構如下圖所示:

圖2 處理器系統視圖

3.2 SOPC動態局部重構系統實現方案

Xilinx已推出支持動態重構的FPGA產品,其Virtex-II Pro和Virtex-4、Virtex-5系列產品中已內嵌了PowePC處理器內核和內部配置訪問通道(internal configuration access port,ICAP)。ICAP是配置FPGA內部結構的配置接口,為動態局部重構技術在片上可編程系統(system on programmable chip,SOPC)的應用提供了基本條件。

本方案利用PowerPC對OPB(on-chip peripheral bus)總線上掛的IP模塊進行重構,從而實現了真正意義上的動態局部重構。

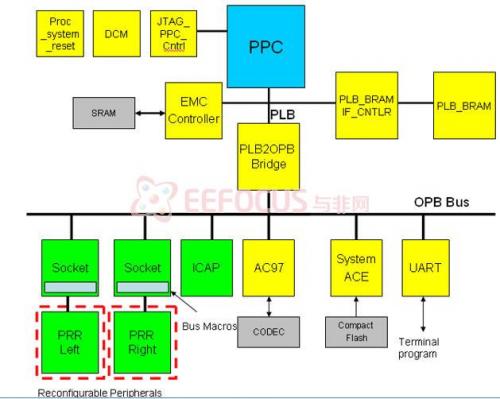

PRR Left和PRR Right為動態重構對象,它們被封裝成兩個掛在OPB總線下的IP模塊,然后構建支持重構的SOPC系統,所構建的SOPC系統結構如圖3所示:

圖3 SOPC動態局部重構系統

其中,PRR Left和PRR Right是動態局部重構的IP模塊;ICAP是掛在OPB總線下的IP模塊,用來加載局部重構配置數據;System ACE是用來存放局部重構配置數據的Compact Flash與OPB總線的接口模塊;UART負責與PC通信,顯示輸出。

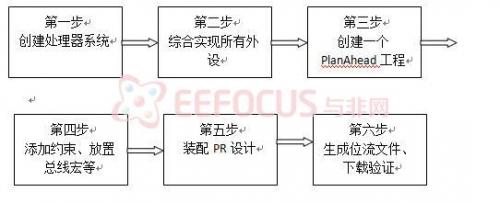

局部重構時,為了防止重構過程中局部重構操作破壞OPB總線的時序、保證重構前后PowerPC時序的連續性,先斷開PRR Left/PRR Right與OPB總線的連接,再將Compact Flash內的重構配置數據寫入ICAP。配置結束后,將PRR Left/PRR Right與OPB總線重新連接,最后對PRR Left/PRR Right模塊進行復位操作,這樣就完成了基于SOPC的動態局部重構。具體的設計和實現流程如圖4所示:

圖4 基于SOPC的動態局部重構流程圖

3.2.1用嵌入式開發套件EDK構建處理器系統

在上文中的局部重構建立完成后,用Xilinx EDK工具構建處理器系統,圖3中所示的掛在OPB總線上的IP模塊都將以外設的形式加載到處理器系統中。其中,ICAP、System ACE、UART模塊都有成熟的IP核提供,利用EDK中的Create or Import Peripheral工具將PRR Left和PRR Right兩個IP模塊以自定義IP核的形式加入到處理器系統中。

3.2.2 綜合實現所有外設模塊

借助Xilinx ISE工具綜合實現所有外設模塊,應該注意的是在綜合過程中,只有頂層模塊的I/O緩沖在綜合時打開,其它子模塊的I/O緩沖在綜合時是不能打開的。

3.2.3 利用PlanAhead手工修改布局布線和裝配PR設計

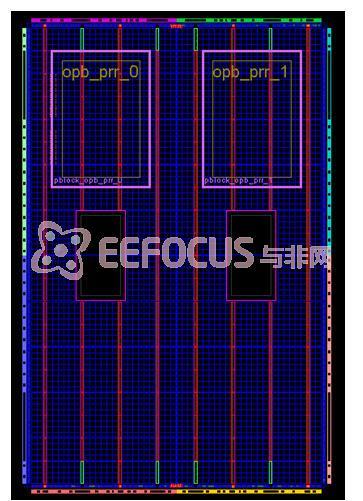

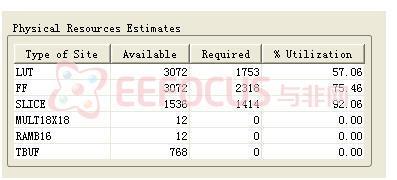

可重構模塊硬件資源分配以及硬件資源分配評估、添加時序和管腳的約束都應該在這一步成功完成。利用PlanAhead工具和ISE集成的FPGA editor工具能夠準確觀察到整個FPGA底層的布局布線圖,同時借助PlanAhead工具直觀看到可重構模塊和靜態模塊的布局布線圖以及它們的資源占用情況[4]。圖5所示的是系統的布局布線圖,圖6所示的是資源分配的情況。

圖5 系統的布局布線圖

圖6 PRR Left重構模塊的資源占用統計

在總線宏busmacros、全局時鐘邏輯等手工放置好之后,將進入裝配階段,將所有靜態邏輯和局部重構邏輯整合到位流文件中。在生成FPGA的初始化位流文件和局部重配置文件之后,利用EDK的Launch EDK Shell工具來生成加載FPGA時需要的System ACE文件。下一步就可以上板調試了。

評論