基于ISA總線的通用多DSP目標系統

(1)目標系統的地址分配與實現

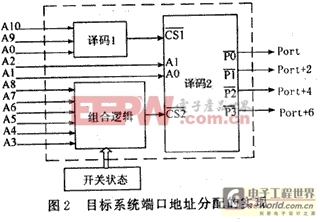

每塊DSP目標板只占用一組端口地址,每組地址共4個:數據端口、地址端口、復位端口和控制端口。組起始地址通過4b跳線開關加以選擇,設開關值為n,則板卡起始地址為360-4×n(記作port),其他3個端口地址分別為port+2,port+4,port+6。在FPGA中采用如圖2所示的邏輯,實現了目標系統板端口地址的動態分配。

|

數據端口port 用于實現對DSP內部存儲器的讀寫操作,完成DSP與上位機之間的數據傳輸。

地址端口port+2 用于提供對DSP進行讀寫操作時DSP內部程序存儲區(PM)或數據存儲區(DM)的起始地址。

復位端口port+4 用于對DSP進行復位操作,實現對DSP的軟復位。

控制端口port+6 用于選擇要操作的DSP。

(2)控制信號的形成

目標板上6片DSP占用同一端口地址,系統工作時,可以對任意DSP的任一數據區進行讀寫操作。對DSP的片選信號是通過對控制端口的操作來實現的。當A2A1=11時,對應于DSP的控制端口,這時數據線的低3位(DATA[2..0])用于指定6個DSP中的一個。

4 下載軟件設計

ADSP2181片內集成了一個可以訪問其內部存儲器的16 b IDMA端口,主機通過此端口可以訪問ADSP2181片內的程序存儲器和數據存儲器的任一單元,實現對DSP下載文件、傳輸數據等操作,這一過程是通過上位機對DSP的IDMA端口的操作來完成的。本文設計了基于VB的通用多DSP目標系統的下載軟件,通過上位機對目標系統進行各種操作。

(1)端口選擇 選擇一組端口地址,他應與目標板的端口地址相一致;

(2)處理器選擇 選擇所要進行讀寫操作及下載的處理器號(1#~6#);

(3)下載文件選擇 選擇要加載到指定DSP的程序;

(4)下載 執行下載操作,并自動檢查加載是否成功,若不成功,則重新加載;

(5)讀處理器選擇 調用讀處理器模塊,讀選定處理器的指定單元的內容;

(6)寫處理器選擇 調用寫處理器模塊,在所選的處理器的指定單元寫入數據。

5 結 語

通用多DSP目標系統,在地址分配上充分考慮到了ISA總線和定點ADSP2181的特點,采用地址的動態分配技術,有效地節省了系統的資源。下載軟件可以對1片或多片DSP進行文件下載、讀、寫等操作,極大地增強了系統的通用性與靈活性。該系統可用于各種算法的硬件平臺和早期研發,具有較高的應用價值。

評論