FPGA與外部存儲設備的接口實現

DRAM性能簡介

DRAM與SRAM不同,它只能將數據保持很短的時間。為了保持數據,DRAM 必須隔一段時間刷新一次,如果存儲單元沒有刷新,數據就會丟失。SRAM雖不需刷新,但斷電后會丟失數據。SRAM的數據傳輸速率從10 ns到30 ns不等,DRAM要比它慢30 ns左右。因此,SRAM通常用于高速緩沖存儲器,而DRAM通常用來存儲較大的數據。HY57V281620HC(L/S)T是4Banks 2M 16bit的同步動態存儲器,性能特點包括:

1.工作在3.3 0.3V電壓下;

2.所有器件管腳都與LVTTL接口兼容;

3.所有的輸入和輸出操作都是在時鐘CLK上升沿的作用下進行;

4.通過UDQM或者LDQM來實現數據延時功能;

5.內部有四個bank可以進行操作;

6.自刷新功能,刷新周期為4096;

7.可編程的猝發類型、猝發長度;

8.可編程的的CAS延遲為2或3個時鐘周期。

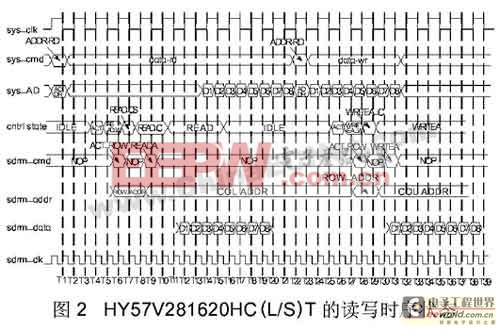

由上面的特性可知,DARM的讀寫操作與SRAM有較大的不同。根據HY57V281620HC(L/S)T的讀寫狀態的時序要求,其讀寫時序狀態如圖2所示:

|

設計實現

當設計FPGA與SRAM的接口時,由于它的傳輸速度較快,所以只需著重考慮如何保證存儲數據的正確性,而不需要考慮用其它方式來提高SRAM的存儲速度。本設計的做法是一次性寫滿128k數據后,再一次性讀出128k數據。為了保證數據的正確性,要求在寫數據時不能讀數據,而在讀數據時不能寫數據。

當設計FPGA與DRAM的接口時,為了能滿足各種系統的使用要求,本設計創建了時鐘頻率、猝發長度、延時節拍等可編程參數。在具體操作DRAM時,首先,必須進行初始化配置,即寫模式寄存器,以便確定DRAM列選延遲節拍數、猝發類型、猝發長度等工作模式。然后通過ACT命令激活對應地址的組,同時輸入行地址。最后,通過RD或WR命令輸入列地址,將相應數據讀出或寫入到對應的地址。操作完成后,用相關命令中止讀或寫操作。在沒有操作的時候,每64ms必須對所有存儲單元刷新一遍,防止數據丟失。

下面本文將指出在設計實現中需要特別注意的幾個問題,并給出了相應的解決方法 。

首先,是如何控制SRAM的讀寫功能。這就需要與IS63LV1024讀寫時序要求和真值表的描述相配合。本設計為了避免連讀或連寫數據時出錯,考慮了一種通過讀寫數據請求的方法來盡量避免讀或寫數據出錯的可能。即每寫完或讀完一個數據后都要先進行請求,然后才能繼續讀或寫數據。ASRAM的狀態轉移圖如圖3所示:

下面給出了圖3中各個狀態所表示的意思:

DOREAD表示讀數據的請求;

DOWRITE表示寫數據的請求;

STIDLE表示存儲器處于空閑狀態;

STWRITE1表示存儲器處于寫準備狀態,準備寫數據;

STWRITE2表示存儲器處于寫狀態,開始寫數據;

STREAD1表示存儲器處于讀準備狀態,準備讀數據;

STREAD2表示存儲器處于讀狀態,開始讀數據。

只有當系統時鐘的上升沿到來時,才會觸發這個狀態機改變一次當前狀態。

剛開始時,存儲器的初始狀態為空閑狀態,當有請求來時才判斷是讀或寫請求,如果沒有請求就一直保持空閑狀態。虛線表示自動按順序進入下一個狀態。

評論