FPGA與外部存儲設備的接口實現

引言

當今社會是數字化的社會,隨著微電子技術的發展,設計與制造集成電路的任務已不完全由半導體廠商來獨立承擔,設計師們更希望在教研室里就能驗證所設計的電路功能。FPGA的出現,使得芯片設計和應用跨入了一個新的領域。

研究背景

隨著硬件方面的急速發展,與之相配套的軟件也不斷更新,更快﹑更智能的原理圖編輯﹑設計實現和驗證工具都被集成到EDA開發工具中。這些發展大大縮短了FPGA的開發周期,增強了FPGA設計的靈活性和可移植性,也避免了專用集成電路設計的高風險。但由于片內存儲器受器件規模和生產成本的制約,其容量通常不能滿足用戶實際需求,這就需要使用半導體存儲器件來擴展存儲空間。針對這種情況,本文專門研究了FPGA與兩種典型的存儲器接口實現問題。在設計實現中采用了Xilinx公司Virtex-E系列的FPGA (XCV300E)﹑ISSI公司的高速靜態存儲器IS63LV1024和HYNIX公司的HY57V281620HC(L/S)T動態存儲器。

XCV300E性能介紹

FPGA(現場可編程門陣列)是可編程邏輯器件的一種,它不僅可以提高系統的可靠性,使得系統結構更加緊湊,節省了電路板的面積,而且實現成本低﹑開發周期短,是進行原始設計的理想載體。Virtex-E系列產品對所有Virtex特性都進行了加強,采用領先的0.18 m六層金屬互連半導體工藝制造,大大提高了器件性能和密度,同時還提供了可進一步滿足下一代數據通信和DSP應用帶寬要求的高性能系統特性組合。Xilinx公司的VirtexE XCV300E,采用BGA432封裝,片內Block RAM為131,072 比特,Distributed RAM為98,304比特,System Gates為411,955門,Logic Gates為82,944門。特性如下:

1.工作在1.8V電壓下的快速﹑高密度FPGA器件 ;

2.采用高度靈活的I/O選擇技術,支持20種高性能接口標準;

3.采用高性能的鏈路選擇技術;

4.精密復雜的存儲器選擇機制;

5.高性能的時鐘管理電路;

6.具有能平衡速度與密度的靈活性體系結構;

7.基于SRAM方式的系統配置。

SRAM性能介紹

為了能更好﹑更有效的設計FPGA與IS63LV1024的接口實現,必須先了解IS63LV1024的性能特點。充分利用這些特點會使設計的實現變得事半功倍。IS63LV1024是128K 8的高速靜態存儲器,性能特點包括:

1.工作在3.3V電壓下,高速接入時間一般分為8、10、12和15ns;

2.高性能﹑低功耗器件(使用ICSI高性能COMS技術制作過程和使用新的電路設計技術);

3.通過選擇CE和OE的狀態可以比較簡單的實現存儲;

4. CE可以使器件進入power-down工作模式,即 沒有被選擇時,器件進入一種掛起狀態,使得功率消耗小于250 W;

5.不需要時鐘和更新,是全靜態工作過程;

6.所有的輸入和輸出都是與TTL相兼容的。

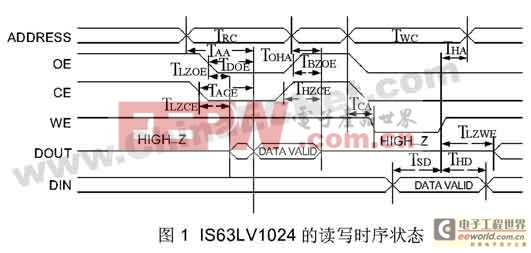

除此之外,為了保證所傳輸的數據的正確性還必須要了解IS63LV1024的讀寫狀態的時序和使能的要求。其讀寫時序狀態如圖1所示:

|

評論