基于NiosII軟核處理器的步進(jìn)電機(jī)接口設(shè)計(jì)

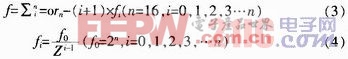

式中:f為要得到的頻率;fi為各個(gè)疊加頻率;f0基準(zhǔn)脈沖;rn-(i+1)第n-(i+1)個(gè)寄存器。

文中取n=16,所以16個(gè)寄存器組成的16位二進(jìn)制數(shù)的范圍就是0000~FFFF。根據(jù)公式(3)、(4)可知,只要f0等于65 536 Hz,那么通過(guò)改變二進(jìn)制數(shù)(r15~r0),輸出f就連續(xù)可調(diào)。該電路也就是脈沖發(fā)生器(step_wave)中的核心電路。

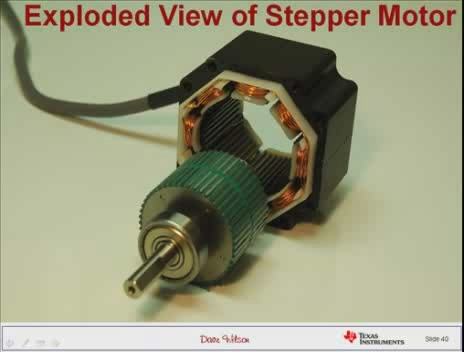

2.3 電機(jī)控制模塊設(shè)計(jì)

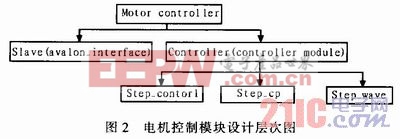

一般步進(jìn)電機(jī)的控制器可以通過(guò)單片機(jī)來(lái)實(shí)現(xiàn),本文電機(jī)控制模塊是用verilog HDL語(yǔ)言實(shí)現(xiàn)、以IP模塊的形式封裝在SOPC Builder的IP模塊庫(kù)中,它是可以被NiosII系統(tǒng)直接調(diào)用的。圖2為電機(jī)控制模塊的設(shè)計(jì)層次圖。

1)脈沖控制器

根據(jù)脈沖控制器要實(shí)現(xiàn)的功能,可以確定脈沖控制器主要是由以下幾個(gè)小模塊構(gòu)成:標(biāo)準(zhǔn)頻率產(chǎn)生模塊;總輸出脈沖數(shù)控制模塊;輸出的脈沖個(gè)數(shù)寄存器更新模塊。

2)脈沖發(fā)生器

脈沖發(fā)生器的功能是產(chǎn)生需要的脈沖序列,經(jīng)過(guò)分析后知道,此部分主要由以下幾個(gè)模塊構(gòu)成:

①16 bit計(jì)數(shù)器,脈沖發(fā)生器最終輸出的脈沖其實(shí)是由1/2CLK、1/4CLK、1/8CLK…1/32 768CLK這16種脈沖組合實(shí)現(xiàn),CLK是由step _control分頻得到基準(zhǔn)時(shí)鐘。為了實(shí)現(xiàn)這16種頻率的脈沖,需要16bit的計(jì)數(shù)器。16bit計(jì)數(shù)器的產(chǎn)生16種狀態(tài),保持16種基頻的狀態(tài)唯一。

②基頻產(chǎn)生模塊,由公式(3)、(4)可知,這16種脈沖其實(shí)是以16bit計(jì)數(shù)器的16種不會(huì)重疊的狀態(tài)為條件而產(chǎn)生的。

③脈沖疊加,脈沖疊加模塊,用來(lái)把這16種脈沖疊加起來(lái),得到需要合成的輸出。最終合成的輸出控制可由16個(gè)兩輸入與門(mén)來(lái)實(shí)現(xiàn),一端接輸出脈沖,另一端接對(duì)應(yīng)的脈沖個(gè)數(shù)寄存器。

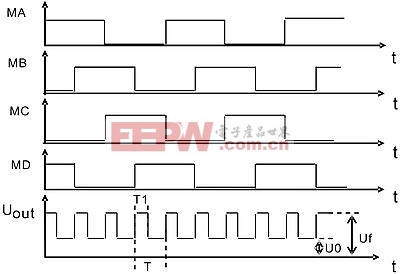

3)脈沖分相器

由于是四相步進(jìn)電機(jī),并以單拍的方式運(yùn)行,所以在最后從脈沖分相器輸出的頻率為四相。CP[3:0]就是最終輸出的四相信號(hào)。

3 電機(jī)控制模塊的仿真與驗(yàn)證

1)功能仿真

電機(jī)控制模塊在Quartus II上的綜合結(jié)果如圖3所示,電機(jī)控制模塊是由slave、step_control、step_wave及step_cp 4部分組成。

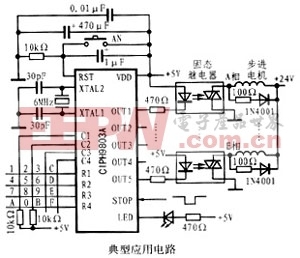

2)SOPC平臺(tái)驗(yàn)證

首先導(dǎo)入的HDL文件是用于描述模塊的硬件邏輯功能。對(duì)于電機(jī)控制模塊,導(dǎo)入的文件分別是motor.v、step_control.v、step_wav e.v和step_cp.V,其中motor.V是頂層文件,配置SOPC平臺(tái),如圖4所示。

評(píng)論