HDTV接收機中Viterbi譯碼器的FPGA實現

2.1 譯碼器的整體實現方案

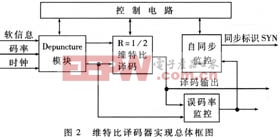

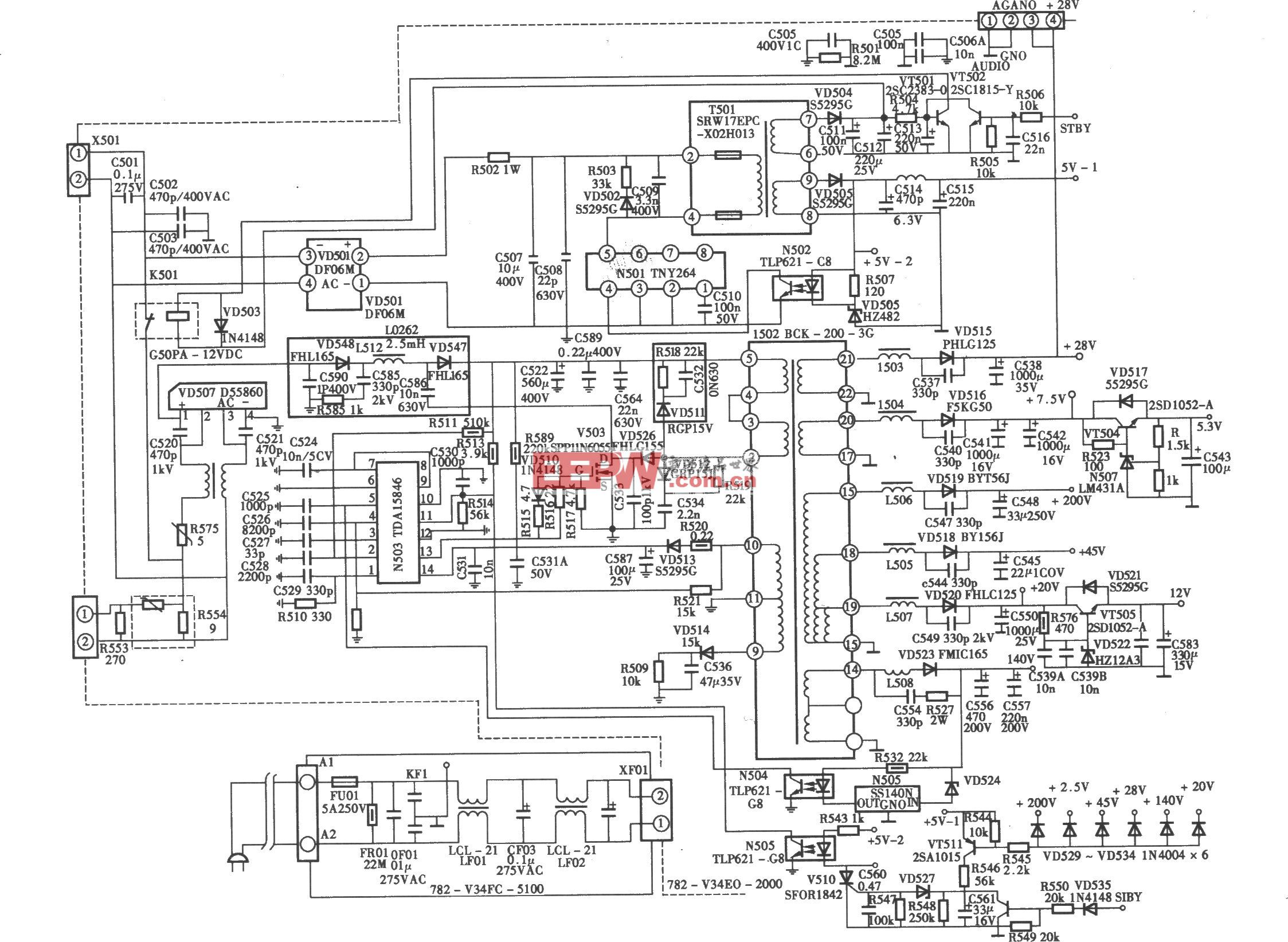

譯碼器的整體方案如圖2所示。

發端的數據經由信道傳輸過來,經過同步和信道估計,根據CSI信息對數據進行維特比量化,將量化后的信息解內交織后送入維特比解碼單元。

接收到前端的碼字后,首先須在發端的刪除位置上填充特定的虛假碼元,這一功能由Depuncture單元來完成。并由該單元產生量度計算禁止脈沖,送入主譯碼器,使譯碼器在譯碼時禁止對這些碼元作量度計算。

主譯碼器的譯碼輸出送到誤碼率監控單元,通過對誤碼率的統計來判定數據是否為同步接收,同時將該信息送入自同步監控單元,以供調整同步使用。當整個譯碼系統同步后,將輸出一同步標識,表示系統已經同步,同時通過同步單元維持同步態。

2.2 譯碼器分模塊的實現

2.2.1 R=1/2的維特比譯碼模塊

根據上述VB算法,對于一個軟判決譯碼器,應具備以下幾部分:

(1)度量值寄存器:用來存儲各路徑的度量值。其前級還應有一狀態發生器,產生64個狀態和分支值。

(2)累加器、比較器和判決器。分別用來進行軟距離的累加,比較各路徑度量值的大小并選擇輸出信息元的值。

(3)路徑寄存器:用來存儲幸存路徑。

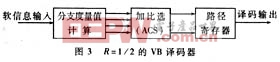

模塊設計如圖3示。

分支度量值計算部分,首先根據接收的軟判決信息計算出每一時刻各分支度量值,在Depuncture模塊輸出禁止脈沖的位置不能進行度量值運算。將該結果送入加比選電路,由表1所得的各狀態間轉移時的輸出分別累加分支度量,并利用比較和選擇電路得到留選路徑,把此信息送入路徑寄存器。當路徑寄存器中64個狀態的路徑度量相等時,經過大數判決電路輸出譯碼信息,送入下級的誤碼監控和自同步電路。

2.2.2 Depuncture電路

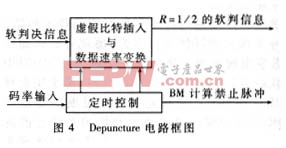

在發端經編碼和刪除后的數據具有大于1/2速率的數據率。為了不增加譯碼器的難度,采用如圖4所示結構的Depuncture電路,把數據速率變回1/2,并在約定的位置插入虛假碼元。通過定時控制電路來確定插入虛假比特的時刻,同時產生禁止計算脈沖,與生成的并行數據一起送入下級。

2.2.3 自同步電路

在傳輸數據的過程中,以2/3碼率為例,它的傳輸序列格式為"X1Y1Y2",即刪除了"X2"位置的碼元。在接收到的軟判決信息序列中,首先必須確定"X1"位置的數據,否則就無法確定插入虛假碼元的位置。而"X1"這一起始信息系統無法傳送,在本設計中自同步電路就是來完成捕獲"X1"這一功能的。如圖2后半部分所示,譯碼器先假定任一位置為"X1",通過譯碼結果結合誤碼監控來判斷是否同步,并把這一信息反饋給Depuncture電路,同步標識SYN為高則表明電路同步,前級就會維持該同步;否則,前級電路將會繼續捕獲,直至電路同步。

評論