基于CPCI總線的FPGA加載設計

PCI9656 的局部總線有M、C、J 三種接口模式,為了簡化數據傳輸控制邏輯,設計中采用了C 模式,該接口模式為適合大多數處理器的通用模式。在數據傳輸中,PCI9656 傳輸數據有兩種模式:突發模式和直接內存存取(DMA,Direct Memory Access)模式。其中突發模式一般用于傳遞少量不連續數據的場合,DMA模式則用于傳遞大量連續數據的場合。

在設計中,所有的參數上傳、下載都是通過突發模式傳輸的,而三片V5 芯片的加載,連續處理數據的上傳則是通過DMA 模式完成的。

3 FPGA 加載概述

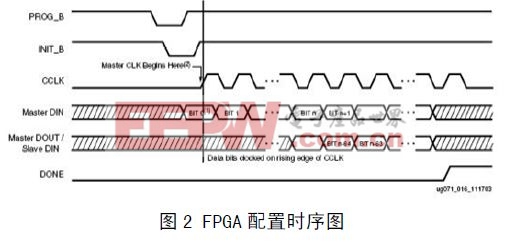

FPGA 的加載有多種模式,主要有主串模式(Master Serial),從串模式(Slave Serial),邊界掃描模式(Boundary Scan),SPI 模式和SelectMap 模式等。設計中采用了Slave Serial 模式,該模式由外部處理器或控制器提供時鐘,總共用到了CCLK,PROG_B,DONE,INIT_B,DIN 5 個管腳,其中CCLK 管腳為加載提供時鐘,當PROG_B 信號置低300ns后檢查INIT_B信號為高電平即可通過DIN管腳送入數據進行加載,當數據加載完成后檢查DONE管腳為高電平表示配置完成。Slave Serial 模式的時序圖如圖2 所示。

FPGA 的配置文件有多種不同的格式,例如BIT,BRT,BIN,MCS,EXO,TEK,HEX 等。由于ISE 軟件調用Bit Gen 程序直接生成的文件格式為BIT,故系統如能直接用BIT 文件作為配置文件將省去文件轉換的麻煩,通過分析發現BIT 文件與BIN(直接二進制配置文件)文件相比僅僅多了文件頭,又由于FPGA 配置過程中會進行同步、器件ID 檢查等操作,因此多出的文件頭部分會自動忽略,故而通過Slave Serial 方式直接下載BIT 文件配置FPGA 是可行的。

4 硬件模塊設計

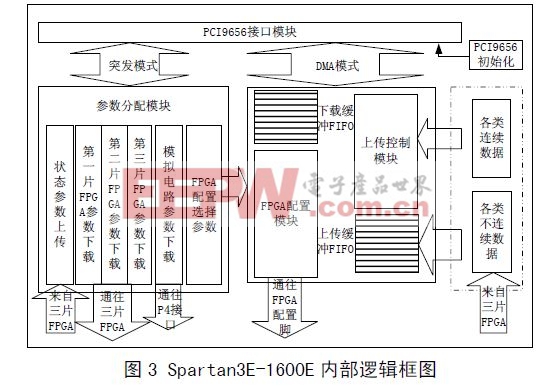

Spartan-3E中的程序設計包含PCI9656配置模塊,負責對PCI9656 芯片進行初始化;PCI9656 接口模塊,負責與PCI9656 進行數據交互;參數模塊,負責將接收的參數重新分配給三個芯片或者將一些狀態信息上傳到工控機;FPGA 配置模塊負責將接收到的FPGA 的BIT 文件流通過FIFO 將不連續數據緩沖為連續數據,并觸發配置邏輯,對FPGA 進行配置。

系統的模塊劃分如圖3所示。

4.1 PCI9656 配置模塊

PCI9656 一般都有對應的EEPROM,用于上電時初始化芯片工作的相關參數。根據實際需求,由于需要初始化的參數較少,PCB 設計中沒有放置EEPROM,需要Spartan-3 E 通過本地總線對其進行初始化。對于PCI9656,初始化其PCI Subsystem ID、PCI Subsystem、Vendor ID 后,在工控機就可以進行其他配置,配置這兩個參數只需要通過本地總線往地址0X2C寫入相應數據即可。

評論